【转】AMBA学习笔记——协议演进概述

0赞原文地址:https://www.cnblogs.com/uiojhi/archive/2018/07/31/9366884.html

随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大。数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用。在基于IP复用的SoC设计中,片上总线设计是最关键的问题。为此,业界出现了很多片上总线标准。其中,由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。

AMBA 1只有ASB和APB协议;

AMBA 2引入AHB协议用于高速数据传输;

AMBA 3,为适应高吞吐量传输和调试引入AXI和ATB,增加高级可扩展接口,而AHB协议缩减为AHB-lite,APB协议增加了PREADY和PSLVERR,ASB由于设计复杂而不再使用;

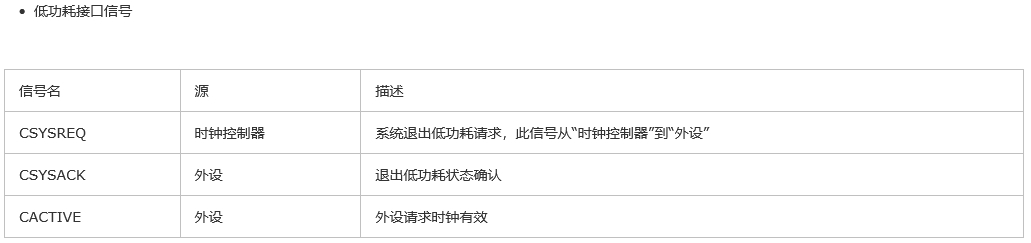

AMBA 4,AXI得到了增强,引入QOS和long burst的支持,根据应用不同可选AXI4,AXI4-lite,AXI4-stream,同时为满足复杂SOC的操作一致性引入ACE和ACE-lite协议,APB和ATB也同时得到增强,比如APB加入了PPROT和PSTRB,另外为改善总线数据传输引入QVN协议;

适应更加复杂的高速NOC设计,引入环形总线协议,推出的AMBA CHI协议。

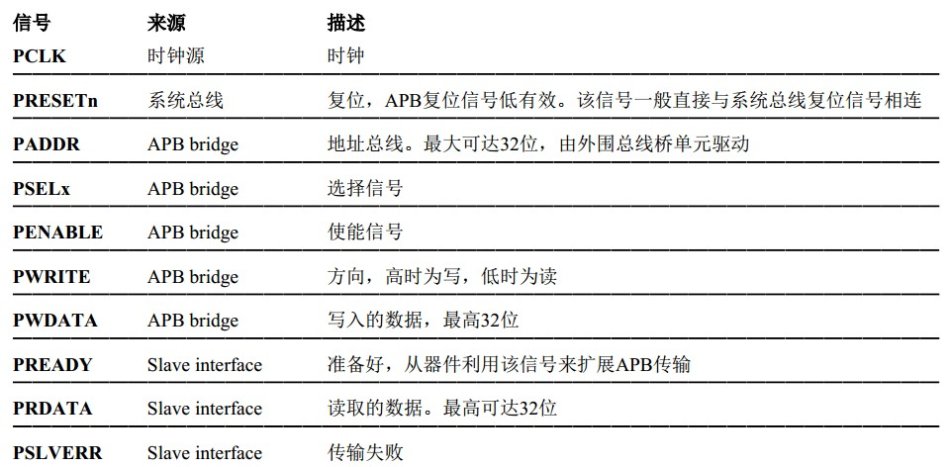

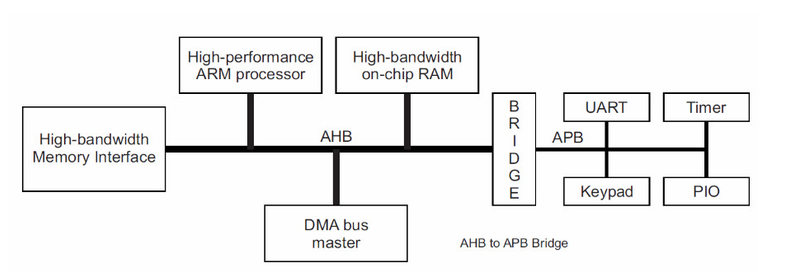

V1.0 ASB、APB是第一代AMBA协议的一部分。主要应用在低带宽的外设上,如UART、 I2C,它的架构不像AHB总线是多主设备的架构,APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些Request/grant信号。APB的协议也十分简单,甚至不是流水的操作,固定两个时钟周期完成一次读或写的操作。其特性包括:两个时钟周期传输,无需等待周期和回应信号,控制逻辑简单,只有四个控制信号。传输可用如下状态图表示,

系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。

当有传输要进行时,PSELx=1,PENABLE=0,系统进入SETUP状态,并只会在SETUP 状态停留一个周期。当PCLK的下一个上升沿时到来时,系统进入ENABLE 状态。

系统进入ENABLE状态时,维持之前在SETUP 状态的PADDR、PSEL、PWRITE不变,并将PENABLE置为1。传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

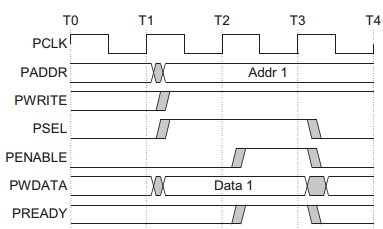

1、写传输包括无等待状态和有等待状态

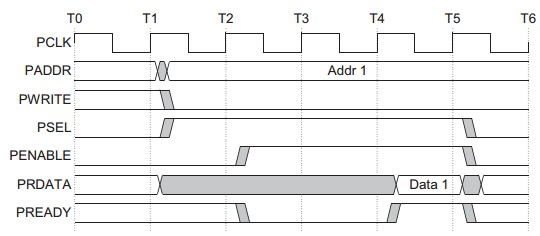

无等待状态地址、写入数据、写入信号和选择信号都在时钟上升沿后改变。第一个时钟周期叫做Setup phase。 下一个时钟沿后使能信号PENABLE被置位,表示Access phase就位。地址、数据和控制信号在Access phase期间有效。传输在该周期后结束。使能信号PENABLE, 在传输结束后清空。 选择信号PSELx同样被置低,除非紧接着下一传输开始。有等待状态右图当PENABLE为高,传输可以通过拉低PREADY来扩展传输。

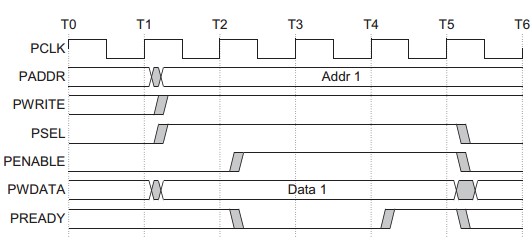

2、读传输包括无等待状态和有等待状态

无等待状态从器件必须在读传输结束前提供数据。有等待状态在Access phase期间PREADY信号拉低,则传输被扩展。

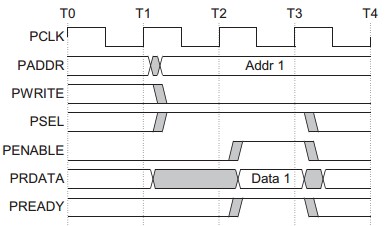

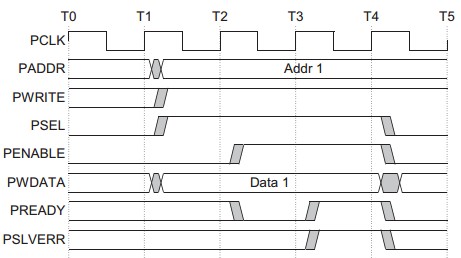

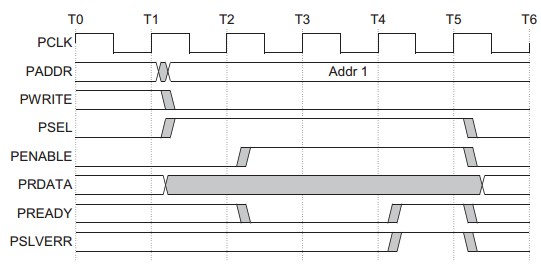

3、传输失败的例子

使用PSLVERR来指示APB传输错误。当PSEL, PENABLE以及PREADY 都为高时,PSLVERR才在最后一个周期进行判断。 当任何一个PSEL, PENABLE或者PREADY为低时,你可以将PSLVERR拉低,这是推荐,并不是强制要求。 收到一个错误后,可能或不可能改变外围器件的状态。 APB外围设备不要求必须支持PSLVERR引脚,当不使用该引脚时,应被置低。

左图为写传输失败最后一个传输周期,PSLVERR信号拉高,右图为读传输失败,没有读出数据。

AXI桥接到APB: AXI的RRESP/BRESP = APB的SLVERR(read: PSLVERR -> RRESP[1], write: PSLVERR -> BRESP[1])

AHB桥接到APB: PSLVERR被映射到HRESP = ERROR(PSLVERR -> HRESP[0])

V2.0 AHB是第二代AMBA协议最重要的一部分。AHB总线规范是AMBA总线规范的一部分,AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。APB用于连接外部设备,对性能要求不高,而考虑低功耗问题。ASB是AHB的一种替代方案。

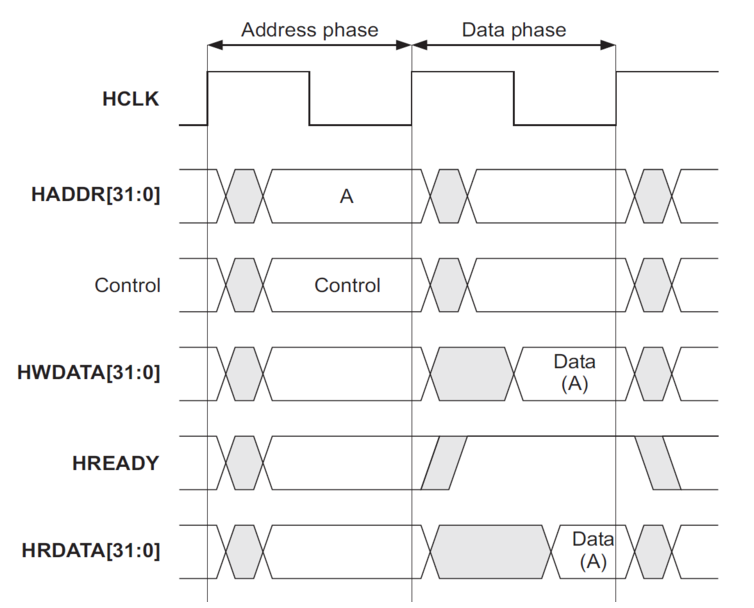

相比于APB,区分了地址周期和数据周期。

AHB总线强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线控制器,以及各种AHB接口的控制器等连接起来构成一个独立的完整SOC系统,还可以通过AHB-APB桥来连接APB总线系统。

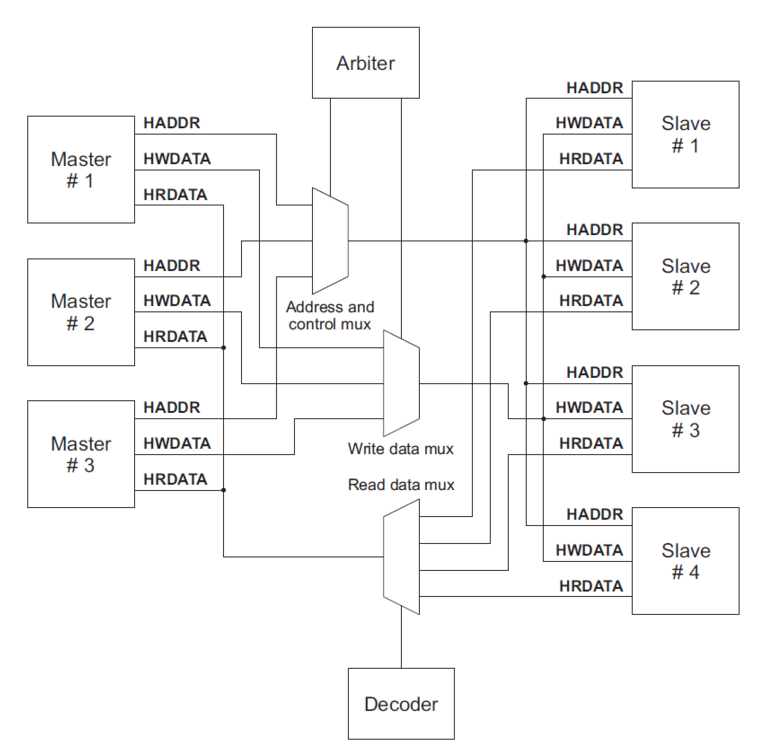

AHB总线由主设备Master、从设备Slave,内部包括仲裁器,译码器,数据多路和地址控制多路组成。

主设备发起一次读/写操作,某一时刻只允许一个主设备使用总线。

从设备响应一次读/写操作,通过地址映射选择使用哪一个从设备。

仲裁器允许某一个主设备控制总线

译码器通过地址译码决定选择哪一个从设备

仲裁机制 仲裁机制保证了任意时刻只有一个master可以接入总线。arbiter决定哪个发出接入请求的master可以接入总线,这通过优先级算法实现。AHB规范并没有给出优先级算法,设计者需要根据具体的系统要求定义。一般情况下arbiter不会中断一个burst传输,将总线接入权让给其他master。当然未定义长度的burst传输是可以打断的,这要看优先级算法是如何规定的。如果一笔burst被打断,master再度获得接入权限时,会传递剩余的部分。如一笔长度为INCR8的传输在传递3 beat后被打断,master再次获得接入授权后,会继续传输剩余的5 beat,剩余部分可以由一个SINGLE和一个INCR4组成,或者一个INCR。

地址译码器 地址译码器用于为总线上每个slave提供选择信号HSELx,选择信号是通过组合逻辑对地址码译码产生的。只有当前的数据传输完成后(HREADY为高),slave才会采样地址和控制信号以及HSELx。在一定条件下可能会出现这样的情况:产生HSELx信号而HREADY为低,在当前传输后slave会改变。每个slave最小的地址空间为1KB,所有的master的burst传输上限也是1KB,如此设计保证了不会出现地址越界问题。当一个设计不会用到所有的地址空间时,可能出现访问到一个不存在的地址的情况,这就需要增加一个附加的默认slave来为上面的情况提供一个响应。当SEQ或NONSEQ传输访问到一个不存在的地址,默认slave应该提供ERROR响应;当IDLE或BUSY传输访问到一个不存在的地址,默认slave会响应OKAY。地址译码器会带有实现默认slave的功能。

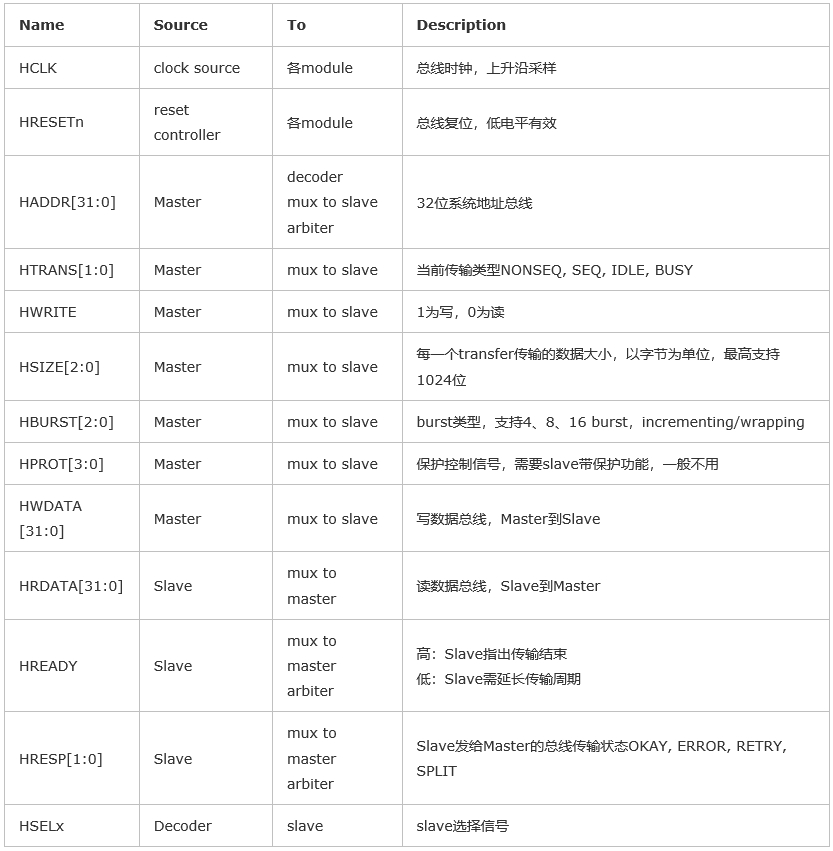

各个信号描述:

HRESP[1:0] 响应信号

传输响应HRESP[1:0]

00: OKAY

01: ERROR

10: RETRY

传输未完成,请求主设备重新开始一个传输,arbiter会继续使用通常的优先级

11: SPLIT

传输未完成,请求主设备分离一次传输,arbiter会调整优先级方案以便其他请求总线的主设备可以访问总线

AHB仲裁信号

总线操作过程

有需要占用总线的主设备向仲裁器发出请求,仲裁器授权给指定的总设备,任一时间周期只有一个主设备可以使用总线,对其指定的从设备进行读写操作。

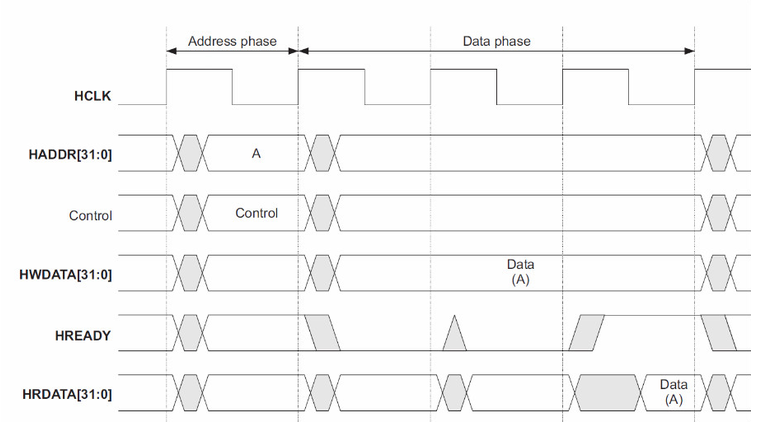

获得授权的总线开始AHB传输,首先发出地址和控制信号,提供地址信息(HADDR)、传输方向、带宽(HSIZE)和burst类型信号(HBURST)。总线统一规划从设备的地址(HSELx),译码器根据地址和控制信号确定某个从设备与主设备进行通信。数据传输通过数据总线完成,不出现三态总线,AHB将读写总线分为读总线和写总线。每次传输包括一个地址和控制周期,一个或多个数据周期。地址和控制周期不能扩展,从设备必须在一个周期内采样地址信号,数据周期可以通过HREADY信号扩展,这点与前面的APB的PREADY信号实现有等待信号传输一样。HREADY为低时给传输加入一个等待状态以使从设备获得额外的时间提供或采样数据,从设备通过响应信号HRESP反映传输状态,AHB-APB桥连接APB总线系统时,PSLVERR被映射到HRESP = ERROR(PSLVERR -> HRESP[0])。

1、没有等待状态和有等待状态的单次传输

第一个周期的上升沿,主设备驱动地址和控制信号

第二个周期的上升沿,从设备采样地址和控制信号,并将HREADY拉高;

如果是写操作,主设备会在第二个周期的上升沿传输要写入的数据,

读操作,从设备会在HREADY信号拉高后将读取的数据写入总线;

第三个周期的上升沿,如果是写操作,主设备获取HREADY高信号,表面从设备接收成功;读操作,主设备获取HREADY高信号表明读数据有效并且接收成功。

HREADY在数据有效期间必须始终为高,并且延续到第三个周期的上升沿之后,确保主设备正确采样。

右图可通过拉低HREADY信号扩展数据周期;写操作时主设备需要在等待时间内保持写数据不变。读数据时,从设备不需要一开始给出数据,等待HREADY信号拉高时给出数据即可。

2、多个单次传输的流水线操作(pipeline)

扩展数据周期的负效应是必须延长下一次传输的地址周期,A和C为零等待传输,B数据加入了一个控制周期,C的地址周期也进行了扩展。

第三个周期主设备发现有操作C需要执行,检查到上一周期的HREADY为高,就将地址和控制信号发送到总线上;同时此时第三个周期上升沿的HREADY信号为低,插入等待状态,B操作执行暂停。

等待状态时写操作已经将数据B写在数据总线上,读操作却不需要提前读取数据B,等检测到HREADY信号为高时,读取数据B到读数据总线上。

需要注意的是,总线上最多存在2个未处理完的传输,只有当总线上未完成的传输少于2个时,主设备才能发起新的操作。

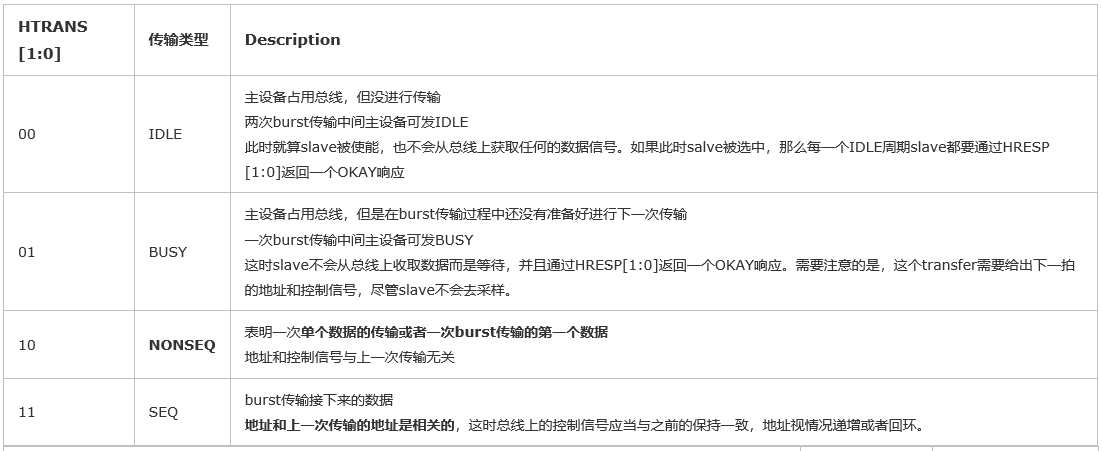

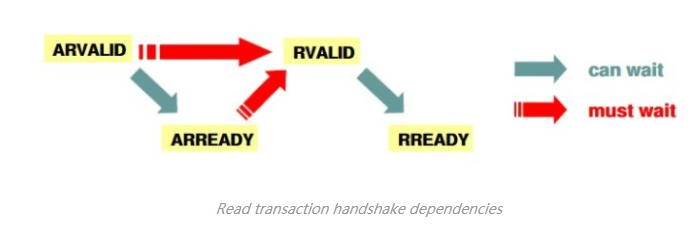

3.相关传输 涉及信号传输类型HTRANS[1:0]、数据尺寸HSIZE[2:0]、Burst传输类型

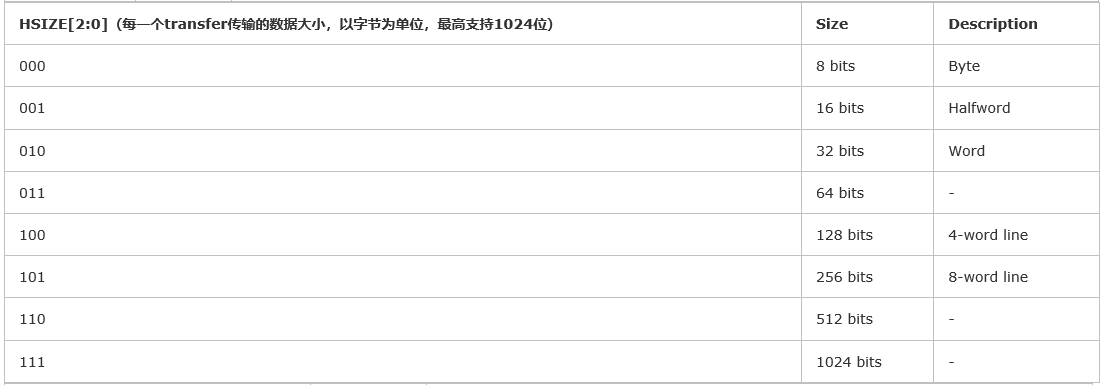

4、打包4拍传输

HTRANS用来表示单次传输类型,SEQ的地址和上一次传输的地址是相关的

HADDR是一个4拍回环地址,每个地址之间相差4个字节,HSIZE表示单次传输数据大小为“Word”为4个字节,HBURST为WRAP4。

5、无定长数据增量地址传输

T1,master传入地址和控制信号,因为是新的burst开始,transfer的类型是NONSEQ;

T2,由于master不能在第二个周期里处理第二拍,所以master使用BUSY transfer来为自己延长一个周期的时间。注意,虽然是延长了一个周期,但是master需要给出第二个transfer的地址和控制信号;

T3,slave采集到了master发来的BUSY,知道master需要等待一拍,所以slave会忽略这个BUSY transfer;

T3,master发起了第二个transfer,因为是同一个burst的第二个transfer,所以transfer的类型是SEQ;

T5,slave将HREADY信号拉低,告诉master需要等待一个周期

T8时刻完成最后一个transfer。

需要注意的 虽然slave会忽略掉BUSY transfer,但是master也需要给出下一拍的地址和控制信号。

6、增量4拍burst

地址并不是回环地址,HBURST为INCR4。

V3.0 AXI(Advanced eXtensible Interface)是一种总协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分。

高性能、高带宽、低延迟的片内总线

地址/控制和数据相位是分离的,分离的读写数据通道。控制和数据通道分离,就可以不等需要的操作完成,就发出下一个操作,流水线操作,数据吞吐量增加达到提速的作用。

单向通道体系结构,使得片上信息流只是以单方向传输,减少了延时,更小的面积,更低的功耗,获得优异的性能。

1、 AXI的五个通道

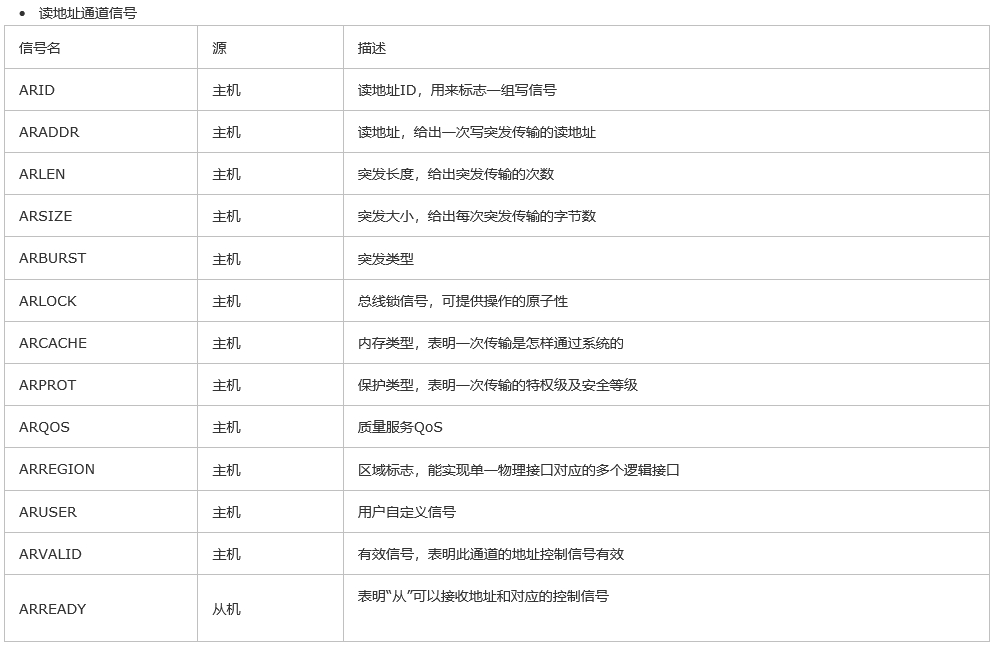

读地址通道,包含ARVALID, ARADDR, ARREADY信号;

写地址通道,包含AWVALID,AWADDR, AWREADY信号;

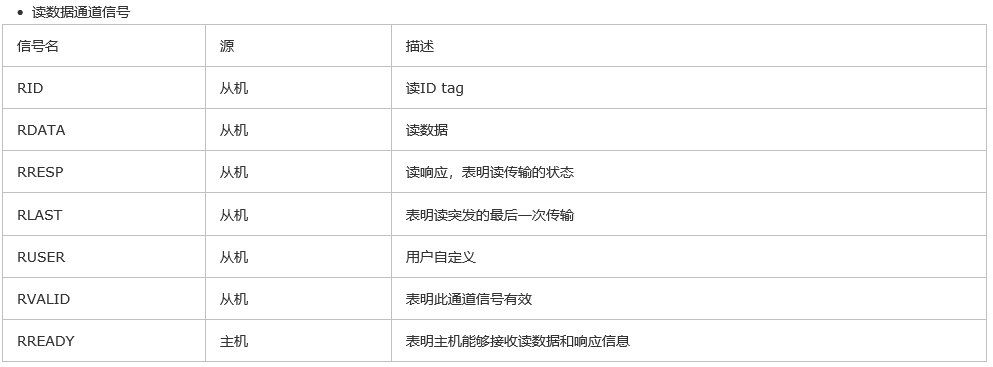

读数据通道,包含RVALID, RDATA, RREADY, RRESP信号;

写数据通道,包含WVALID, WDATA,WSTRB, WREADY信号;

写应答通道,包含BVALID, BRESP, BREADY信号;

系统通道,包含:ACLK,ARESETN信号;

ACLK为axi总线时钟,ARESETN是axi总线复位信号,低电平有效;读写数据与读写地址类信号宽度都为32bit;READY与VALID是对应的通道握手信号;WSTRB信号为1的bit对应WDATA有效数据字节,WSTRB宽度是32bit/8=4bit;BRESP与RRESP分别为写回应信号,读回应信号,宽度都为2bit,‘h0代表成功,其他为错误。

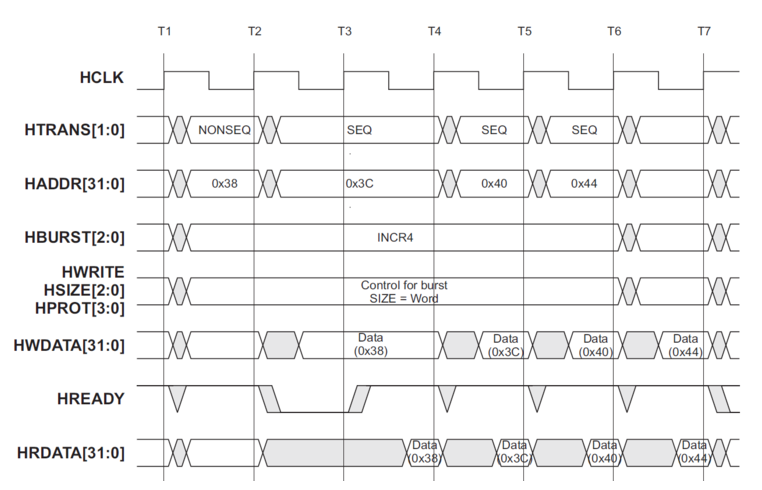

2、握手机制

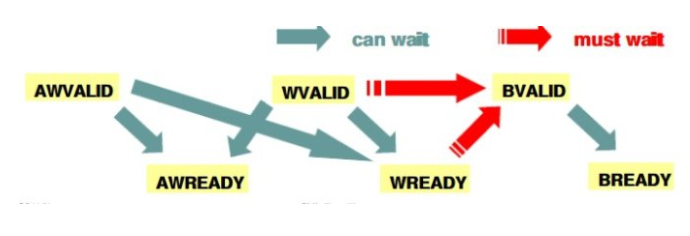

每个channel内的valid和ready之间没有严格的先后顺序,但是channel间的valid和ready信号有依赖关系。对于读操作,spec要求读data必须出现在读addr之后,因此读操作的两个channel之间存在如下的依赖关系,即必须等到ARVALID的ARREADY同时为High后,RVALID才能拉高。

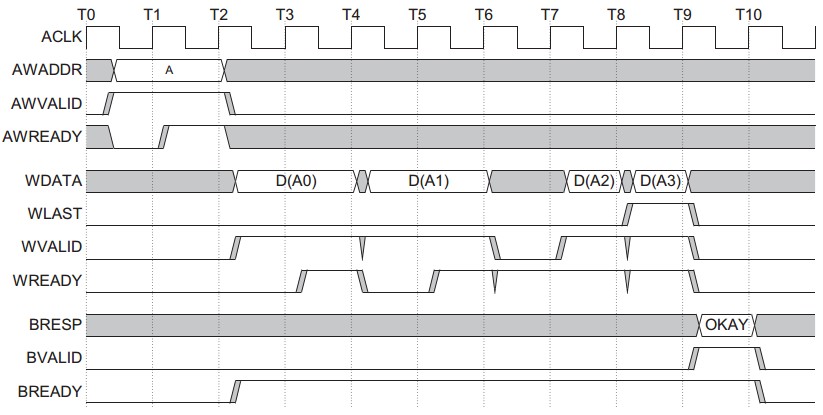

对于写操作,addr和data两个channel之间不存在依赖关系,但是只能等最后一次transfer结束后,才能拉高BVALID。从下图中看不出AWVLAID, AWREAY与BVALID之间的关系,但是,隐含条件是slave只有接收到addr和data后,才能做出响应,因此AWAVLID, AWREADY为High,且最后一次transfer结束后才能拉高BVALID.

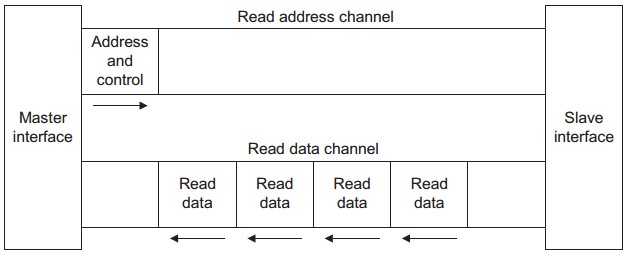

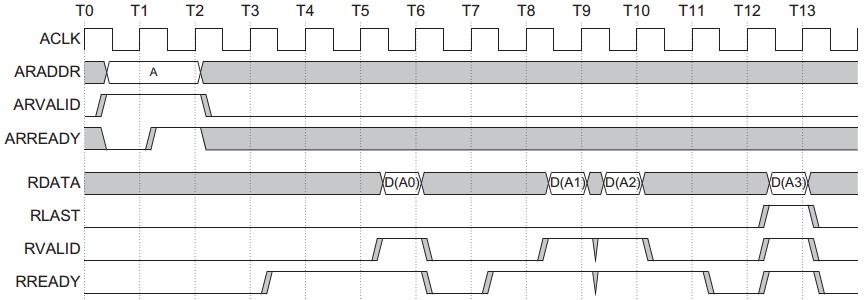

3、读操作

顺序为主与从进行读地址通道握手并传输地址内容,然后在读数据通道握手并传输所读内容以及读取操作的回应,时钟上升沿有效。

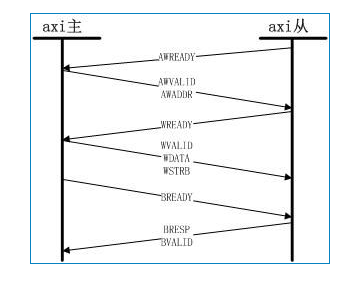

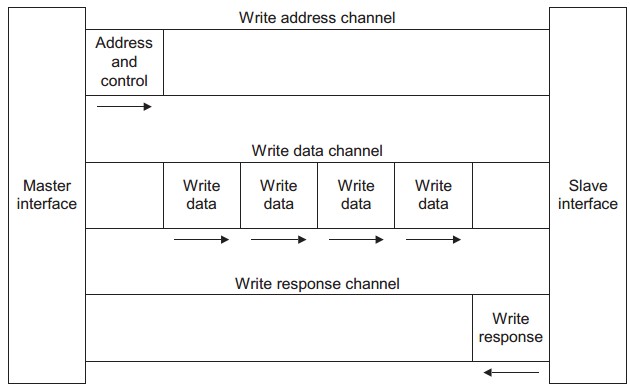

4、写操作

顺序为主与从进行写地址通道握手并传输地址内容,然后在写数据通道握手并传输所读内容,最后再写回应通道握手,并传输写回应数据,时钟上升沿有效。

AXI4 是第四代AMBA协议重要的一部分,AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-streamAXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

适合高带宽低延时设计,无需复杂的桥就实现高频操作,向下兼容已有的AHB和APB接口。

分离地址/控制、数据相位

分离的读写数据通道,提供低功耗DMA

使用字节线支持非对齐的数据传输

使用基于burst的传输,只需传输首地址

支持多种传输方式,支持乱序传输

允许容易的添加寄存器来进行时序收敛

AXI架构分为5个独立的传输通道,读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。数据总线可为(8/16/32/64/128/256/512/1024bit),最大为单次传输一个字节的数据。

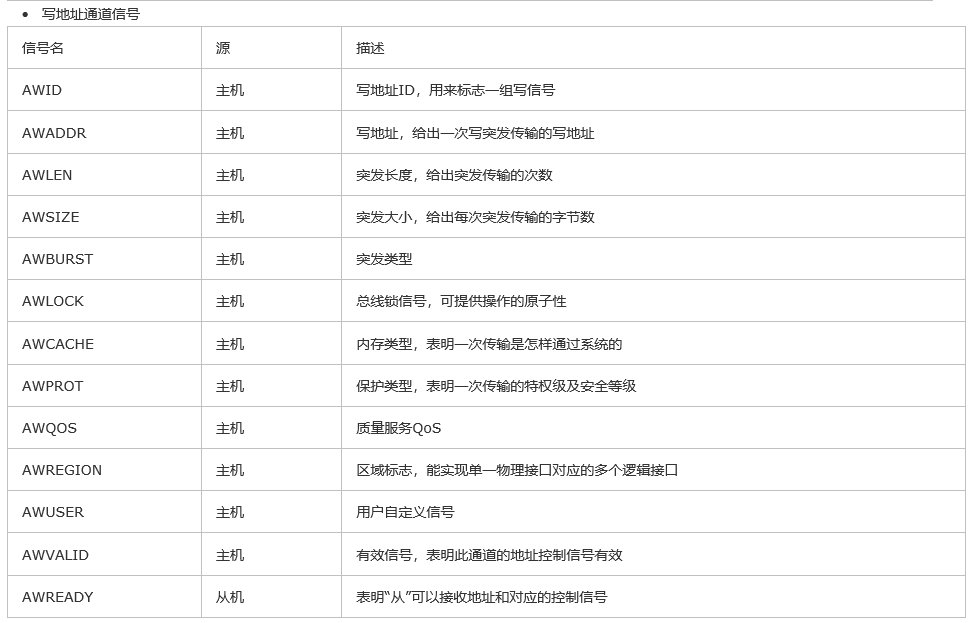

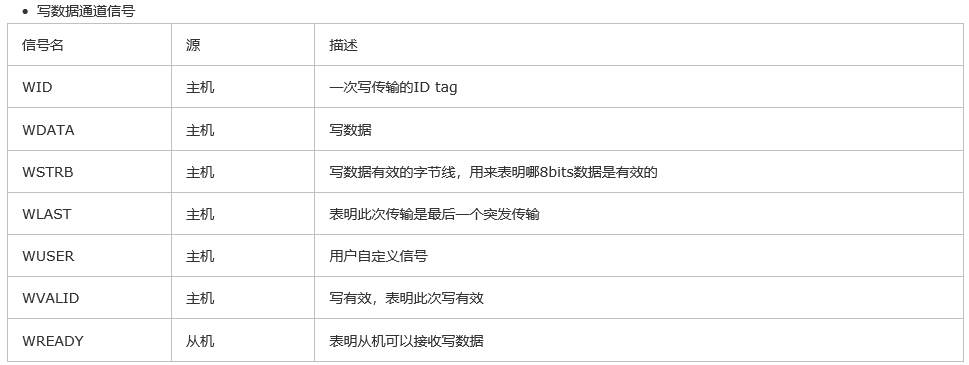

.信号描述

每个数据通道有独立的xVALID/xREADY握手信号对。

VALID与READY信号作为一对握手信号,为防止死锁,进行读操作时,必须等读地址通道握手完成,读数据通道才可进行下一步操作。进行写操作时,写地址通道与写数据通道互相独立,但同样必须等最后一组数据写完成写响应通道握手完成。

AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

突发长度 ARLEN[7:0]决定读传输的突发长度,AWLEN[7:0]决定写传输的突发长度。AXI3只支持1~16次的突发传输(Burst_length=AxLEN[3:0]+1),AXI4扩展突发长度支持INCR突发类型为1~256次传输,对于其他的传输类型依然保持1~16次突发传输(Burst_Length=AxLEN[7:0]+1)。

传输规则 wraping burst ,burst长度必须是2,4,8,16, burst不能跨4KB边界,不支持提前终止burst传输。

突发大小

ARSIZE[2:0],读突发传输;AWSIZE[2:0],写突发传输。

AxSIZE[2:0] bytes in transfer

‘b000 1

‘b001 2

‘b010 4

‘b011 8

‘b100 16

‘b101 32

‘b110 64

‘b111 128

突发类型

FIXED:突发传输过程中地址固定,用于FIFO访问

INCR:增量突发,传输过程中,地址递增。增加量取决AxSIZE的值。

WRAP:回环突发,和增量突发类似,但会在特定高地址的边界处回到低地址处。回环突发的长度只能是2,4,8,16次传输,传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。回环边界等于(AxSIZE*AxLEN)。

AxBURST[1:0] burst type

‘b00 FIXED

‘b01 INCR

‘b10 WRAP

‘b11 Reserved

Start_Address=AxADDR

Number_Bytes=2^AxSIZE

Burst_Length=AxLEN+1

Aligned_Addr=(INT(Start_Address/Number_Bytes))xNumber_Bytes。//INT表示向下取整。

对于INCR突发和WRAP突发但没有到达回环边界,地址由下述方程决定:

Address_N=Aligned_Address+(N-1)xNumber_Bytes

WRAP突发,突发边界:

Wrap_Boundary=(INT(Start_Address/(Number_Bytes x Burst_Length)))x(Number_Bytes x Burst_Length)

读写响应结构

读传输的响应信息是附加在读数据通道上的,写传输的响应在写响应通道。

RRESP[1:0],读传输

BRESP[1:0],写传输

OKAY(‘b00):正常访问成功

EXOKAY(‘b01):Exclusive 访问成功

SLVERR(‘b10):从机错误。表明访问已经成功到了从机,但从机希望返回一个错误的情况给主机。

DECERR(‘b11):译码错误。一般由互联组件给出,表明没有对应的从机地址。

几种AMBA总线的性能对比分析