Vivado之时序约束XDC

1赞xilinx的约束文件主要包含两大类:时序约束(timing constraints)与物理约束(physical constraint)

物理约束主要就是:IO管脚定义,bank电压分配,管脚逻辑电平等。

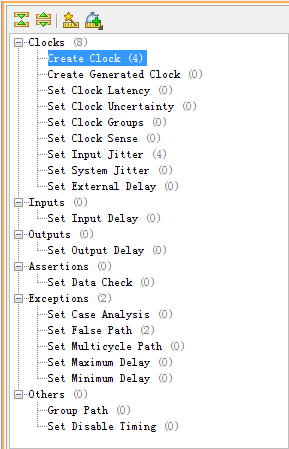

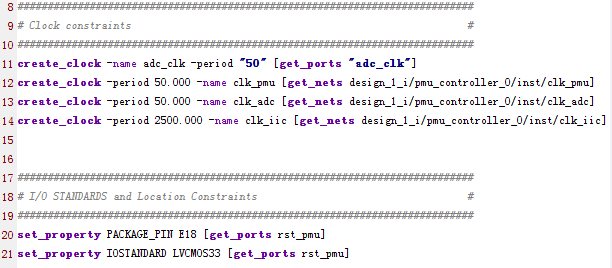

时序约束包含下面这几类,常用的是对clock和delay的定义。每一项都对应一条指令,如create_clock

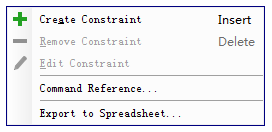

右键这些指令,选Command Reference,查看用法参考

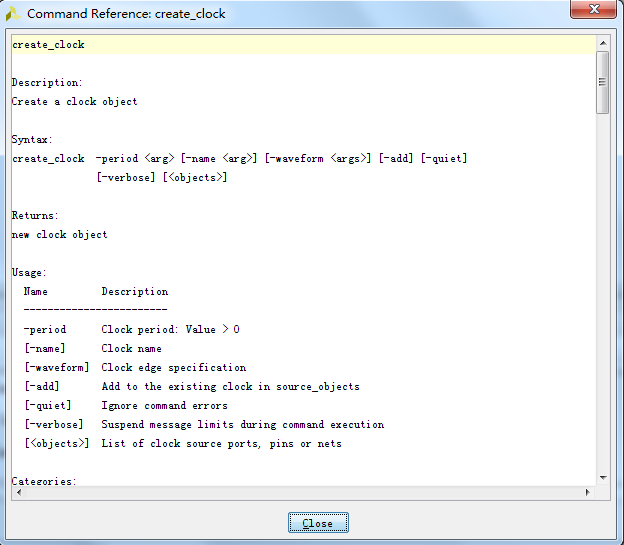

可以直接看到每条指令的功能和用法,免去了找手册的麻烦。

建议大家对照语法说明,以及vivado自带IP核里面的XDC文件,一起来体会这些约束该怎么用。

create_clock -name clk_fpga_0 -period "20" [get_pins "PS7_i/FCLKCLK[0]"]

set_input_jitter clk_fpga_0 0.6

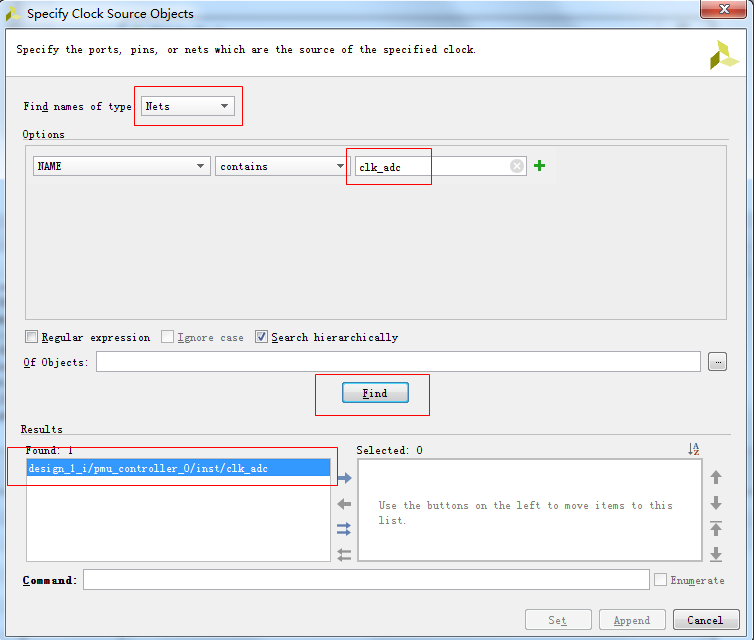

get_ports # I/O ports, FPGA管脚

get_pins # cell pins, 模块接口

get_nets # nets,模块内部net

细节方面请参考xilinx厂家FAE的系列文章:http://xilinx.eetrend.com/article/8441

物理约束示例

# Quad SPI Flash / qspi0_ss_b / MIO[1]

set_property iostandard "LVCMOS33" [get_ports "MIO[1]"]

set_property PACKAGE_PIN "A7" [get_ports "MIO[1]"]

set_property slew "slow" [get_ports "MIO[1]"]

set_property drive "8" [get_ports "MIO[1]"]

set_property pullup "TRUE" [get_ports "MIO[1]"]

set_property PIO_DIRECTION "OUTPUT" [get_ports "MIO[1]"]