多图对比:Vivado与ISE开发流程的差异

0赞为了体现Vivado与ISE的开发流程以及性能差异,本文使用了相同的源码、器件,IP核分别用自己软件下的最新版本例化,时钟及管脚约束完全相同。

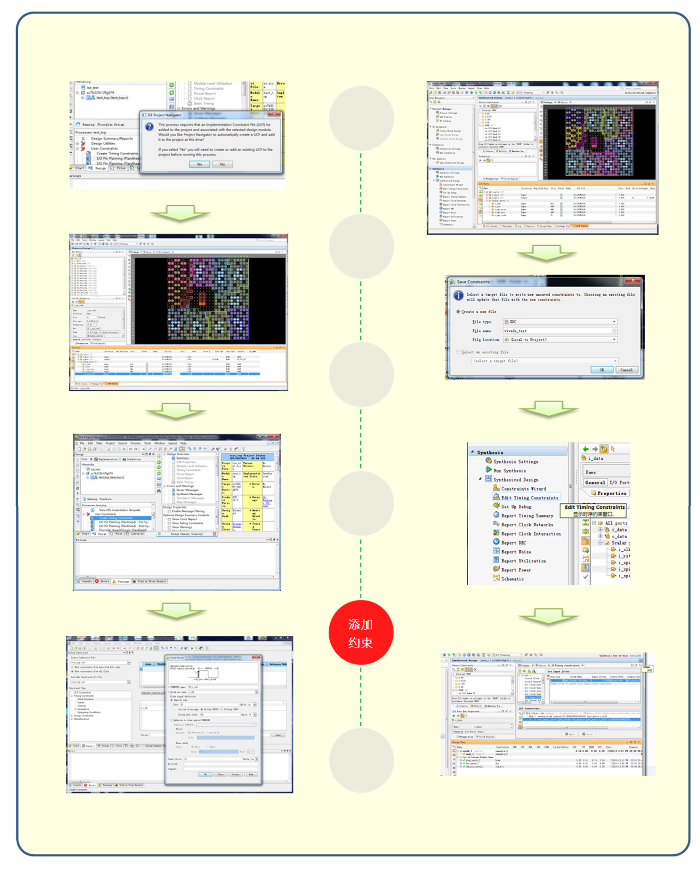

开发流程:

建立工程 -> 加入代码 -> 添加IP核 -> 初步综合 -> 添加约束 -> 综合实现

附:测试用源码 src.rar 感兴趣的童鞋可以自己试下

(点击可看大图)

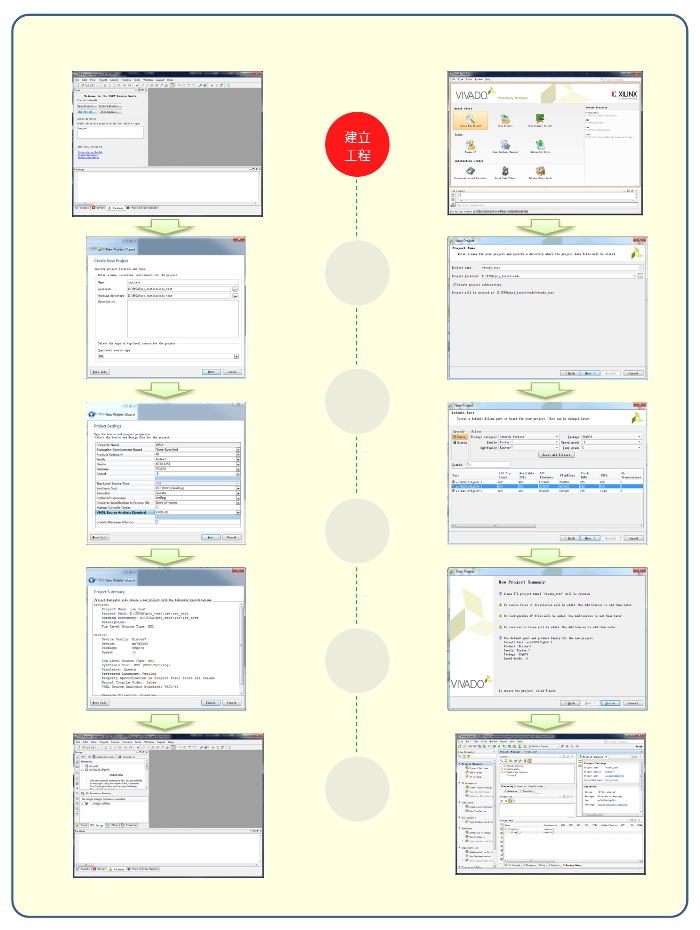

1、建立工程——点评:

Vivado界面清爽,流程清晰,完败Q2。再也不会因ISE的低集成度,再在各组件中调来调去了。

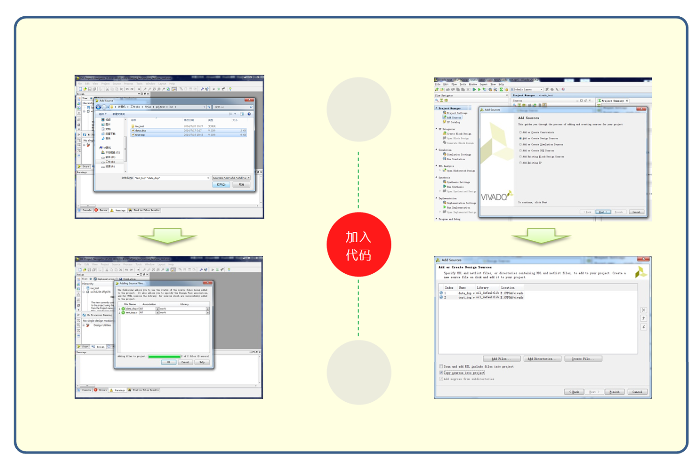

2、加入代码——点评:

Add Source无明显区别。

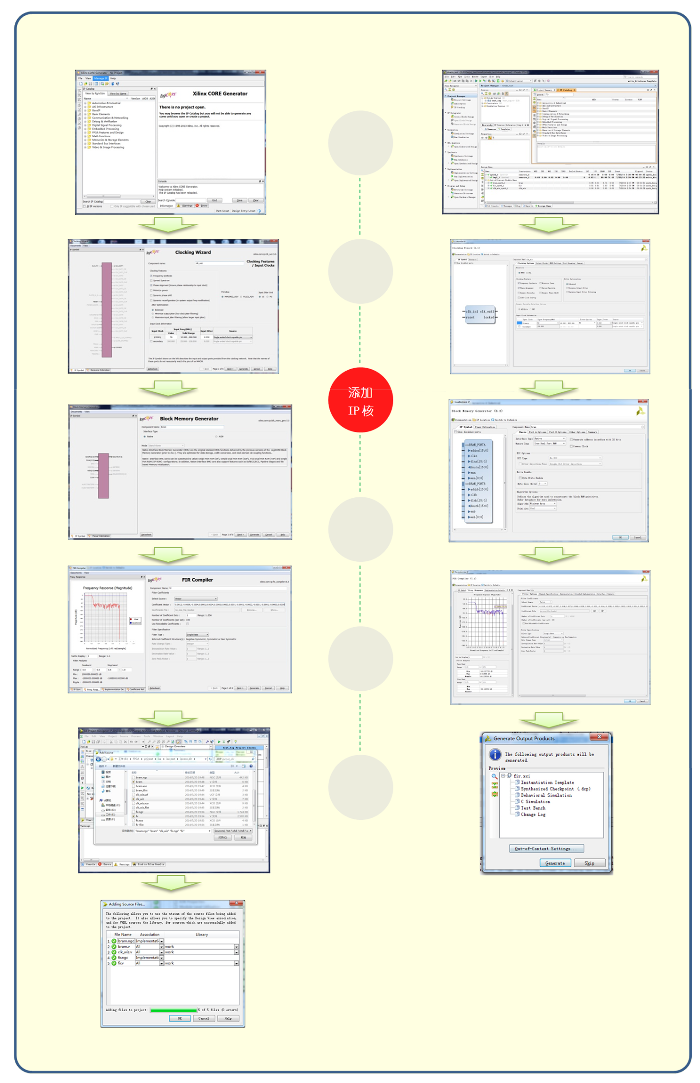

3、添加IP核——点评:

由于core gen没有被ISE集成,即便是从ISE中打开core gen,也需要重新建立core gen工程,甚至需要选择与工程一样的元器件,并且生成IP核之后还需要手动添加到ISE工程内。(为了公平测试综合性能,本例在ISE中直接添加IP核网表文件;Vivado的dcp文件中包括综合网表)

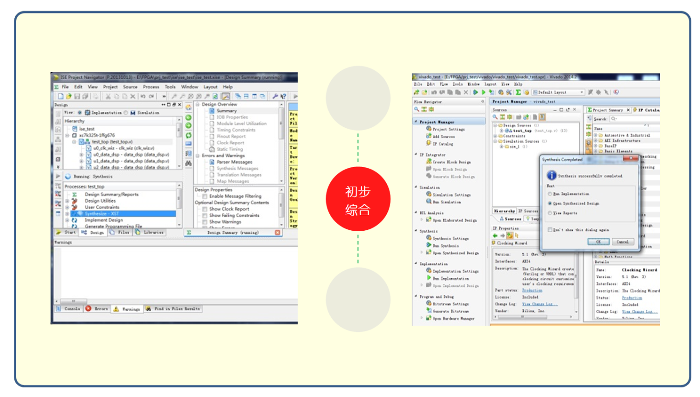

4、初步综合——点评:

在添加约束前,最好先综合,以便明确综合后网表中的clk的名字。Vivado实时检查代码是否存在语法错误,而ISE需要综合的时候才能发现。

5、添加约束——点评:

由于ISE添加MMCM时没有加入自动生成的约束,需要重新添加时钟约束。而Vivado自动将IP核添加到工程内,是包含时钟约束的。为了更好的ISE和Vivado的综合性能,管脚位置与电平约束完全一致。

PS:若时钟和管脚约束直接敲命令,两者除了语法,没有明显区别。

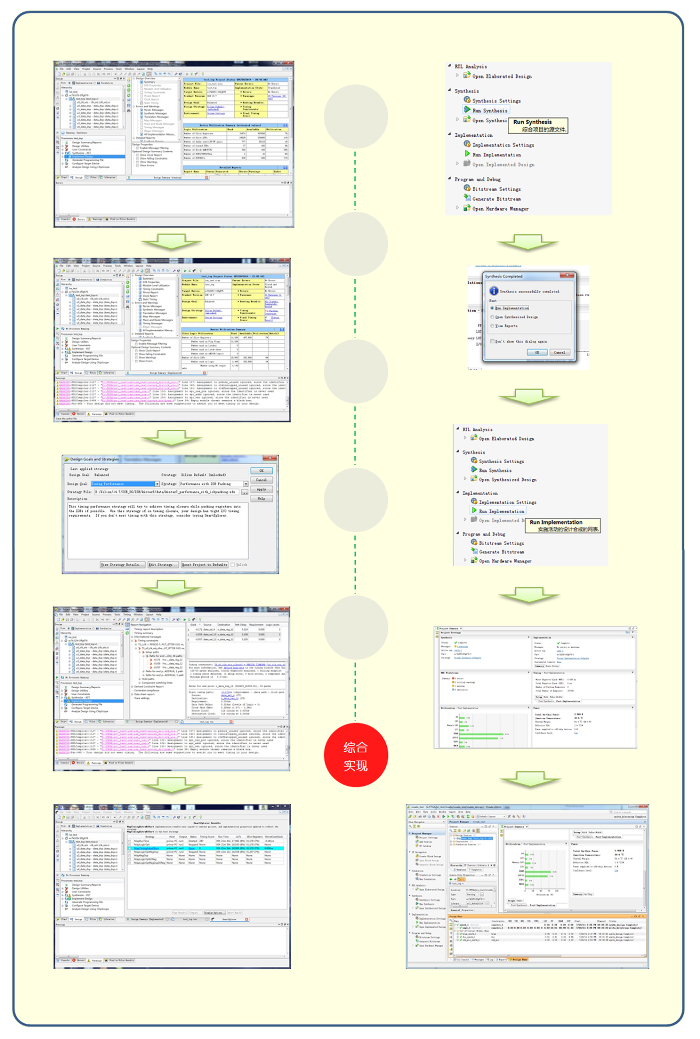

6、综合实现——点评:

Vivado默认策略情况下从综合到生成bit共计23分50秒。而ISE第一遍默认策略情况下,25分钟实现结束,时序约束未过。修改实现策略为Timing Performance,又过了二十五分钟,时序还没有过……最后不得已上大招,SmartXplorer同时跑四个!!!!瞬间CPU占用率,内存利用率爆表- -/// 22分钟后,终于有一个时序通过的结果出现。对比效率,Vivado:ISE =3:1。