Vivado的在综合和实现步骤上的进步

0赞FPGA的设计流程中,出去编写代码,仿真和上板调试,主要的步骤还有综合(Synthesis)和实现(Implementation)。这两部分主要是由EDA工具完成。

综合是FPGA设计中总要的步骤,其直接决定最终是否可以通过测试。而对于实现时遇到的诸多问题,其中许多都需要返回到综合这一步来解决。

ISE的综合工具室XST,在实际使用中,感觉Vivado的综合工具比XST强大很多,对代码的理解和优化更加完善。不过这需要长时间的使用才能感觉出来,从硬性指标来看,Vivado综合工具最大的进步在于,综合器是时序驱动的。

XST在综合时,不会读取ucf文件中的约束,另外,对综合结果的时序分析也是非常不准确, 所以在ISE设计流程中,需要利用map和PAR的努力才能得出较为准确的结果。

而Vivado在综合时就会读取XDC中的时序约束,尽早的分析时序,暴露出潜在的问题,恢复了综合在FPGA设计流程中应有的重要地位。

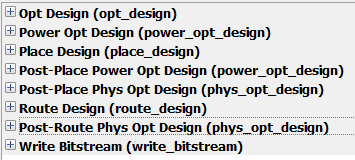

ISE的实现,分为translate,map和PAR三个步骤。通过对Vivado中Implementation Settings中可以看到,Vivdao的Implementation分为Opt Design,Power Opt Design,Place Design, Post-Place Power Opt Design, Post-Place Phys Opt Design, Route Design这几个步骤,其中所有的优化步骤(Opt)都是可选的,这样给予开发者灵活的空间。

由于Vivado软件的整体性比较好,在各个步骤后的时序分析相对准确,所以可以利用Tcl脚本,在各个步骤之间加入Tcl命令,导出各个步骤后的资源、时序及功耗的分析,用来比较分析,既方便调试,也可以加深对Vivado工具的理解。

综上所述 ISE开放给设计者的空间较小,而Vivado主张尽早的暴露问题,让设计中潜在的隐患能够被设计者更快的而发现,也给与设计者更多更灵活的发挥空间。