明德扬至简设计法设计的IP核加法器

0赞

发表于 5/11/2017 5:38:07 PM

阅读(4023)

本案例:明德扬首创全新FPGA设计技巧--至简设计法,教你如何一步一步去完成一个复杂电路的设计,里面很多有实用技巧,熟练运用这些技巧,有助于你写出非常优秀的FPGA设计代码。非常简洁易读,欢迎比较。

明德扬至简设计法设计的IP核加法器,在Quartus II 和ISE中都有加法器的IP core,可以完成无符号数和有符号数的加、减法,支持有符号数的补码、原码操作及无符号数的加、减操作,引入了最佳流水线操作,可以方便的为用户生成有效的加法器,用户可以根据自己的需要来完成配置加法器 ,本案例用Altera和Xilinx的IP核实现了26位加法器的功能。

一、功能描述

在Quartus II 和ISE中都有加法器的IP core,可以完成无符号数和有符号数的加、减法,支持有符号数的补码、原码操作及无符号数的加、减操作,引入了最佳流水线操作,可以方便的为用户生成有效的加法器,用户可以根据自己的需要来完成配置加法器 ,本案例用Altera和Xilinx的IP核实现了26位加法器的功能。

二、平台效果图

Altera仿真效果图

三、实现过程

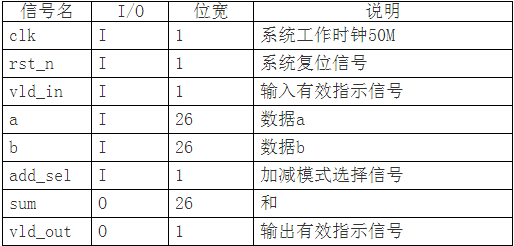

Xilinx输入输出信号列表如下:

用户按照步骤和手册生成IP核后,根据自己的需要来配置设置便可。

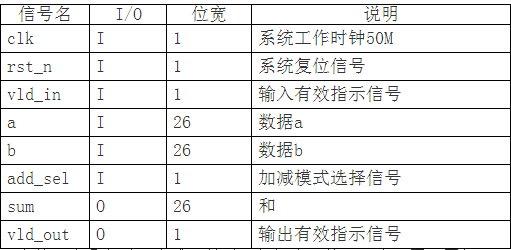

Altera输入输出信号列表如下:

用户按照步骤和手册生成IP核后,根据自己的需要来配置设置便可。

代码资料下载:http://pan.baidu.com/s/1mibRKgC