片上网络小记-2

0赞

感谢上一篇王博的精彩回复,王博后来觉得回复不过瘾还专门发了个邮件详细阐述他的观点。再次感谢王博的大力支持。但从论述的完整性上考虑,还是先按照我的计划把MPSoC说完。

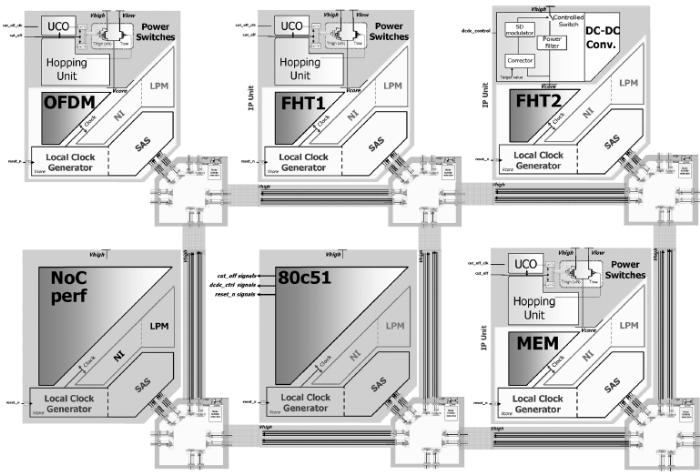

首先就是继续上图,上一点猛图:

这是世界领先的思密达研究院发表在2011年的JSSC上面采用的一个NoC结构。当然,他本质上不是要做NoC,而是要做一个智能图像识别的Chip。思密达研究院做这个项目前后历经N年,从一开始的板级分离模块搭建到最后的单片实现。前前后后有2篇JSSC、1篇ISSCC、1篇CICC和1篇VLSI Symposium。各位请猜一下专门写NoC的那个是哪一篇?

答案揭晓:专门写NoC的那一篇是发的CICC,全称叫:Intelligent NoC with Neuro-Fuzzy Bandwidth Regulation for a 51 IP Object Recognition Processor 。看到这篇就可以找到别的了。

在这里,NoC完全是定制化的,作为一种专用的链接方法而存在的。因此完全是一种ASIC/SoC的设计方法。或者再直接一点说,这个是最极端的application aware的设计方法。

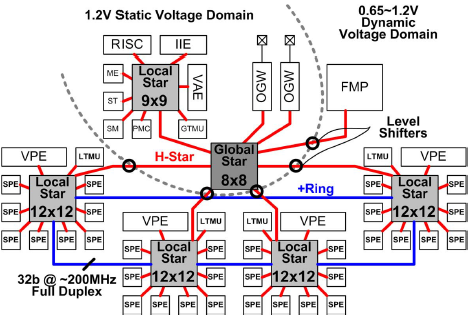

如果说上面的这个玩意确实过于极端了,而且NoC本身发的文章水平不算是顶级的话呢。那么大家可以看一下下面这篇文章里出现的NoC:

这是2009年JSSC文章:An Asynchronous Power Aware and Adaptive NoC Based Circuit 。作为NoC的研究被一向重视电路和器件级研究的JSSC收录是极少的,所以这篇文章应该还是相当不错的。这篇文章的核心在于利用异步的NoC互联各个核心,做了构成了一个复杂的片上系统。其实这个系统也不是很复杂……主要的IP也就几个。这篇文章的主要卖点应该是低功耗和DVFS控制,之前这文章还有一个ISSCC版本。觉得他的功耗调节的电路设计得很巧妙。

当然,说了这么多,其实还要爆一个更加重量级的NoC。这就是ARM公司的Corelink。包括了多个高速处理器内核间为了保证Cache一致性的CCN-504(应该是类CMP架构的NoC)和用于互联处理器核心和外设的NIC400。其中CCN-504是ARM从单核走向多核所必须要解决多核间cache一致性的网络。而NIC则是在SoC从简单SoC走向复杂SoC之后,作为AMBA4.0协议的一种具体的实现形式,重点解决“多主多从”复杂片上系统并行化数据传输的问题。具体的情况大家可以去查看ARM公司的相关资料。

作为一个做SoC的研究者(虽然小G同学认为我只能算是号称做SoC的研究者,她才是做SoC的……Her research is better.) ,其实我对于今天发表的这种NoC的用法更熟悉。什么叫SoC?这个我可以单独找时间来讨论一下。我这里可以简单的总结一句:我认为SoC是以软制硬的ASIC或者以以硬助软的通用处理器。目前大部分的SoC更多的像前者,这些器件也被称为smart XXX。因而NoC在这类应用的里面也更像一种定制化的存在,而非像搞通用计算的那帮人追求的高效通用计算平台。那么这类应用通常都有比较明确的的DFG(数据流图),整个NoC的各种设计指标可以通过计算或者仿真很明确的求得。

其实我真还是很想有机会能做一做这种NoC的,即使它只是整个设计的配角。正如我们强调基于什么AMBA或者其他的什么乱七八糟的的片上协议的SoC,更多的不是在关注那条总线一样。但对于数字系统来说,以接口设计为核心的片上互联子系统设计的虽然看上去“毫无技术含量”,但却是决定系统整体功能能否正常工作的根本。IP-core设计得对不对是很好验证的,IP-core设计得不好其结果无非是数据处理速度不行而已。而如果片上互联子系统设计得有问题,轻则引起各种时序问题,重则导致整个系统无非工作。

当然,这种NoC从学术研究的角度上来说没有什么价值了,太specify 了。所以要进入下一个议题:MPSoC——一种类MPP组织结构的多核系统。