揭秘:DynamIQ是个什么玩意?

2赞最近ARM高调的推出了个“黑科技”——DynamIQ。我们的Tiger主编也到现场去了,本来还说等着他老人家写个报道什么的,结果是左等右等盼不到。但随着其它媒体把这消息慢慢传出来了,我也大概读了一下。这一读,发现还真有点信息量啊!既然Tiger主编不动笔写,那我就自己先出来随便说说了。

DynamIQ这玩意其实包含了四点:一是在最新的V8.3指令集中增加面向人工智能的专用指令;二是在单个集群(Cluster)中支持大小核或异构核;三是实现每个核独立的电压频率调节,也就是所谓pre-core DVFS;四是专门为汽车应用开发用于ADAS的安全可靠的解决方案。

第四点我不是很熟悉,我就前三点展开一下评论。

面向人工智能的专用指令,这个玩意是现在人工智能硬件设计竞赛中的一种解决方案。相比于使用现有的专用处理器(如GPU)作为加速器以及设计专门的硬件加速引擎而言,在指令集上改进无疑是难度最大但灵活性最高的方案。这在目前人工智能算法尚未完全成型还有较大改进空间的当下,无疑具有很大的吸引力。是不是会继DSP、GPU以后又出现一种面向专门领域的处理器,这确实是有很大想象空间的。但这条路无疑也是最艰难的,只有ARM这样又多年处理器研发经验和足够大的生态支持的厂家才能玩得起这套方法。但即便是这样,这套方法的前景依然值得考虑。

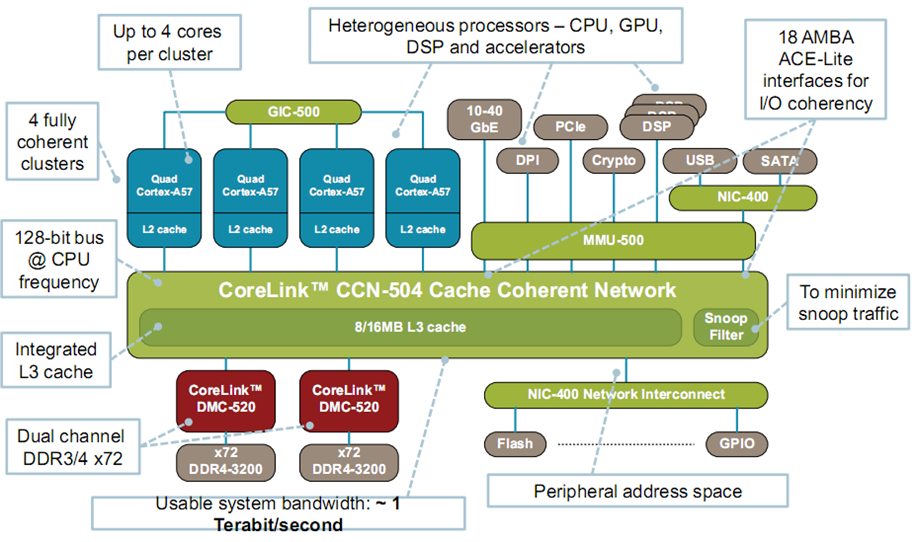

在单个集群中实现大小核甚至异构核,这个问题真是撞到我枪口上了。多年的计算机系统结构的研究,让我对这个问题最为熟悉。我们先来看一张图:

这是目前ARM给出的一种异构多核的体系结构互联方案,从这里很直观的可以看出4个同构的Cortex-A57是作为同一个Cluster的。每个Cluster内部4个(最多)Cortex A57 通过本Cluster的L2 Cache共享数据,而L3 Cache是在各个Cluster之间共享的数据。而DSP、加密处理器(Crypto)这些异构的加速器则是在MMU的管理下被作为一个高速的外设来控制和访问的。在这种架构下面,主处理器与异构加速器之间的数据互通需要从L1到L2再到L3最后通过MMU映射到加速器的存储单元中。而异构加速器那边往往也有一套类似的机制。这就造成了数据处理过程中数据搬移引起的延迟不可避免。这在处理一些实时任务时是不可接受的。我们之前想用FPGA异构计算来加速通信信息处理就是因为这个原因而无法继续下去。因此,在未来嵌入式人工智能的处理中,无论是图像识别、自动驾驶都对实时性都有很高的要求。因此在越低级别的Cache中实现数据的共享,数据搬移引起的延迟越小。显然,在同一个Cluster内部实现数据的共享是延迟最低的。但这个问题同样很难解决,AMD搞APU就一直想解决这个问题。但是一解决就解决了10年。因此这一点到底效果如何,同样需要观察。

第三点是Pre-Core DVFS。每个核可以独立的调节电压和频率是计算机系统结构领域的研究者一早就提出来的设想,而且他们还未这个设想“配套了”很多控制算法。到后来这个不但设想每个核心可以独立的调节电压和频率了,还设想每个片上的路由器也都来调节电压和频率。然而,理想是丰满的,现实是骨感的。到目前为止Pre-Core DVFS不过是一种设想而已。为什么需要搞Big-little的设计,实际上就是对Pre-core DVFS的一种妥协。具体的分析大家可以参考我之前对2016年ISSCC写的评论文章。因此这第三点,还是存疑。

如果ARM真的有能力实现以上三点,那确实是计算机系统结构和处理器设计的一个新时代的开始。意味着系统结构吹了10多年的牛逼有机会变成现实。作为一个系统结构领域的研究者,想想还有点小激动呢。不过到底后事如何,还是得看下回分解。