FPGA 初学者征程(7) 基本组合电路之加法器

0赞

发表于 2015/4/24 13:25:35

阅读(1346)

首先声明一下,前几篇博文老是图片不能看,估计是因为我直接在原来我的新浪博客上复制过导致图片无法查看,因为实在太忙,大家如果有意看的话,前几篇请点击这个链接就OK了:http://blog.sina.com.cn/u/320947

在上一篇博文中我说到了我的modelsim自动退出的问题,我也没找到问题,只是重新装了一下系统就ok了,我不知道什么原因。好了,下面开始我们的技术部分吧。

学过数字电路的朋友都知道数电的电路有两种,组合逻辑和时序逻辑。在下面的几篇博客中将简单的介绍常用的组合逻辑如何用Verilog语法实现,其中包括加法器,比较器,译码器,编码器,数据选择器,数据分配器。

好了我们先来说说加法器,加法器比较简单,就是两个说相加,代码如下;

/* module name :adder_8.v;

module function:8 bits add ;

Author:niceman

contact:18921428564@163.com

weibo :niceman1992

version : v1.0

write date :2015/4/22*/

module adder_8(sum,c,a,b,cin);

output[7:0] sum;

output c;

input[7:0] a,b;

input cin;

assign {c,sum}=a+b+cin;

endmodule

其中cin是上一级运算是否产生进位,可用于加法器的级联,c是这次运算是否产生的进位,

下面是testbench

`timescale 1 ps/ 1 ps

module adder_8_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg [7:0] a;

reg [7:0] b;

reg cin;

// wires

wire c;

wire [7:0] sum;

// assign statements (if any)

adder_8 i1 (

// port map - connection between master ports and signals/registers

.a(a),

.b(b),

.c(c),

.cin(cin),

.sum(sum)

);

initial

begin

a=8'd0;b=8'd0;cin=1'b0;

#10 a=8'd20;b=8'd30;cin=1'b1;

#10 a=8'd30;b=8'd45;

#10 a=8'd138;b=8'd105;cin=1'b0;

#10 a=8'd100;b=8'd215;cin=1'b0;

#100 $stop;

end

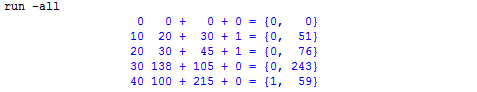

initial $monitor($time,,"%d + %d + %b = {%b, %d}",a,b,cin,c,sum);

endmodule

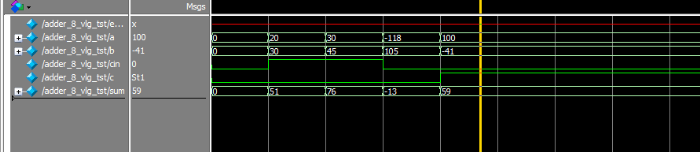

modelsim仿真之后的波形图如下所示

如果大家有什么问题,可以联系我:邮箱:958889621@qq.com