Modelsim仿真流程

0赞

1打开modelsim软件

进入modelsim软件,新建工程file->new->project:

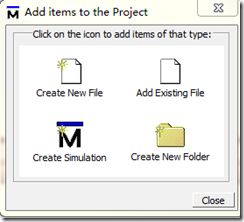

3、要让选择是新建一个文件还是添加已存在的文件,这两个都可以选择,假如事先编好了文件,就选择添加进来,假如没有就新建。在这里使用添加已有文件,在软件开始之前就编好所用的程序,这样比较方便些。软件自带的编辑环境不是很好,使用第三方的编辑工具是推荐的方法。建议使用UltraEdit或Notepad++这些专业的代码编辑软件。

在路径E:\mytest\counter\modelsim下新建两个文件,一个是counter.v,一个是test_counter.v,前者是我们的原始的设计文件,后者是其相应的仿真测试文件。在这个路径的Windows目录下,在空白处右键选择新建一个文本文档.TXT格式,然后在这个文件上右键选择UltraEdit或Edit with Notepad++就可以启动相应的代码编辑工具进行编辑了,保存的时候注意存成“.v”或“.vhd”格式即可。

以下给出两个文件的代码:

第一个文件:

//-----------------------------------------------------

// Design Name : counter

// File Name :counter.v

// Function :8 bits counter with async clear and sync load

// Coder :Cheng xu

//-----------------------------------------------------

module counter (

clk ,

aclr ,

load ,

load_din ,

dout

);

// Port declarations

input clk ;

input aclr ;

input load ;

input [7:0] load_din ;

output [7:0] dout ;

//Internal Variables

wire clk ;

wire aclr ;

wire load ;

wire [7:0] load_din ;

wire [7:0] dout ;

reg [7:0] counter = 0 ;

//Code Starts Here

always @ (posedge clk or negedge aclr)

if (!aclr)

counter<= 0;

else if (load == 1)

counter<= load_din;

else

counter<= counter + 1;

assign dout = counter;

endmodule

第二个文件:

//test_counter.v

`timescale 1ns/1ns //注意最前面的符号是数字键“1”左边

//那个符号,不是单引号

module test_counter();

reg clk ;

reg aclr ;

reg load ;

reg [7:0] load_din ;

wire [7:0] dout ;

initial

begin

clk = 0;

aclr = 1;

load = 0;

load_din =0;

#120 aclr =0;

#40 aclr =1;

#20 load =1;

load_din =100;

#20 load =0;

#100 $stop; //可以不添加这个仿真结束的系统任务

end

always #10 clk = ~clk;

counter U(

.clk(clk),

.aclr(aclr),

.load(load),

.load_din(load_din),

.dout(dout)

);

endmodule

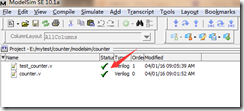

我们接着就可以编译这两个文件了,这时候没有编译文件,所以Status一栏显示的是两个问号。接着在这个Project区域单击鼠标右键,选择“Compile→Compile All”,把HDL源文件编译到当前工程的工作库当中去。

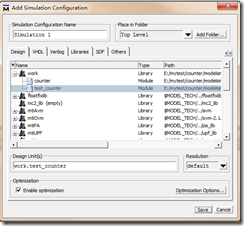

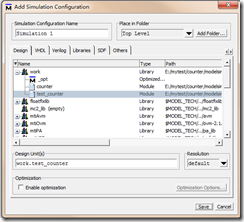

5、编译通过之后,在Project区域鼠标右键点击“Add to Project → Simulation Configuration”

在出现的Add SimulationConfiguration对话框的右下角打开Optimization Options,打开后切换到Options选项卡页面,在Optimization Level中选择Disable Optimizations

点击OK确定之后返回Add SimulationConfiguration对话框,在Optimization栏中关闭Enable Optimization,再展开work目录,选中Test Bench文件test_counter8,之后save保存

会在Project区域出现一个仿真配置文件:Simulation 1,双击它就能进入仿真了,而且重启ModelSim之后,还可以双击它进入仿真,比较方便。

注意:如果不关闭优化选项的话,有时候ModelSim软件会报错导致不能正常进行仿真。

6、双击“Simulation 1”后进入仿真波形界面,在Object区域鼠标右键选择“Add → To Wave → Signals in Region”,把待仿真的信号添加入Wave窗口。

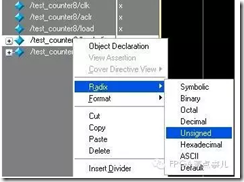

接着我们把wave窗口中的两个信号量改成无符号数显示,方便我们观察,在load_din和dout上依次单击鼠标右键。

7、在Transcript区域中的VSIM提示符后输入命令“run 1us”,把仿真的时间设置为1us。画面会出现我们这个测试文件的内容,还会有个箭头指向我们设置的仿真结束的命令行。实际可以在代码中不添加这个仿真结束的系统任务,我们输入的run 1us命令就已经限定了仿真结束的时间在开始后的1个微秒。如图16所示。我们不管它,直接关掉这个文件,后显示的是我们的仿真波形,

我们在这个波形画面上点一下鼠标的左键,这个时候工具栏上的放大缩小按钮被激活,就是那个放大镜中间带个加号那个是放大的,带减号的就是缩放的,我们把这个图形放大些来看看,或者点击wave窗口右上角的“+”按钮,即“ZOOM/UNZOOM WINDOW”。

我们可以看到这个波形图就是按照我们编写的Test Bench文件来进行测试仿真的,这个8位的计数器在异步复位和同步加载的控制信号下工作完全符合我们的设计要求。

8、仿真过程中如果发现设计不符合要求,此时可以打开UltraEdit或Notepad++对源文件进行修改,保存。再在ModelSim的Project区域鼠标右键选择“Compile→Compile All”,重新编译源文件。之后在工具栏上点击Restart按钮,清除刚才的仿真波形数据。

9、退出仿真时在Transcript区域的VSIM提示符后输入quit -sim就能退出仿真界面,回到工程界面。

功能仿真,又叫前仿真,也是开发过程中最重要、最必不可少的一个环节。相对于前仿真来说,还有一个后仿真,也叫时序仿真。

注意:大型开发和设计中基本都是通过时序约束和时序分析的方法来确保FPGA设计的时序,因为不可能每修改一次代码就做一次时序仿真,这样会相当的费时费力,效率上完全不能满足快速开发的时间要求。通过时序约束和时序分析的方法来确保时序的优势在于,大规模的代码开发中,如果只是个别人修改了部分代码,那么他对自己修改的代码确保功能仿真正常即可合入整个的版本代码中去,时序问题都由大版本中的时序约束来保证,这样就极大地提高了开发的效率。