EMIFA接口

0赞EMIFA为DSP芯片与众多外部设备之间提供一种连接方式,最常见的用途就是同时连接FLASH和SDRAM,

同时可实现DSP与FPGA之间的高速连接。

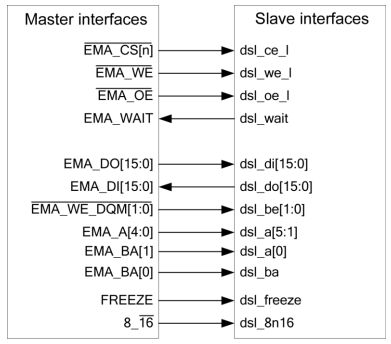

此处,在FPGA内部实现EMIFA接口主从通信,即:主机模块通过EMIFA接口对从机模块(EMIFA接口对外)进行配置或通信。

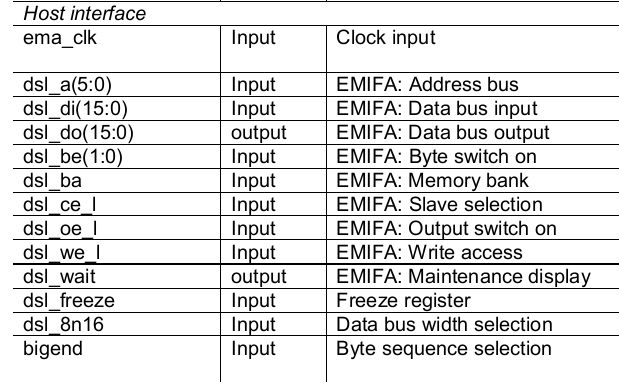

从机接口定义

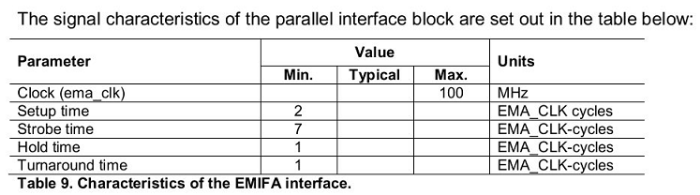

EMIFA 接口参考时序要求

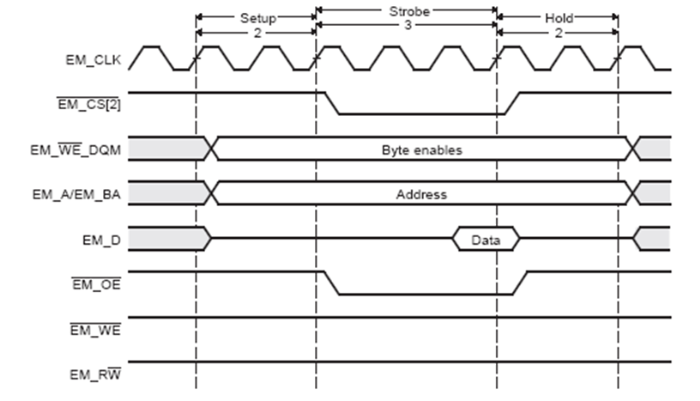

参考时序波形

主状态程序:

assign wr_enable = ( ~init_done ) || long_message_wr_en ;

assign rd_enable = ( init_done_q2 && pos_ready && rd_encoder_data || long_message_rd_data_en ) && link;

//Defining the next state

assign StartIdle = (( ~wr_enable ) & ( ~rd_enable )) | long_message_wr_done

| long_message_rd_data_done | ( rd_cyclic_data_done_q1 && ( !rd_cyclic_data_done_q2 ));

assign StartRdSetup = ( StateIdle | ( StateWrHold & ( clk_cnt == 4'd2 )) | ( StateRdHold & ( clk_cnt == 4'd2 ))) & rd_enable ;

assign StartRdStrobe = ( StateRdSetup ) & ( clk_cnt == 4'd2 );

assign StartRdHold = ( StateRdStrobe ) & ( clk_cnt == 4'd6 );

assign StartWrSetup = ( StateIdle | ( StateWrHold & ( clk_cnt == 4'd2 ) ) | ( StateRdHold & ( clk_cnt == 4'd2 ))) & wr_enable;

assign StartWrStrobe = ( StateWrSetup ) & ( clk_cnt == 4'd2 );

assign StartWrHold = ( StateWrStrobe ) & ( clk_cnt == 4'd6 );

assign WrDone = StateWrHold & ( clk_cnt == 4'd1 );

assign RdDone = StateRdHold & ( clk_cnt == 4'd1 );

always @( posedge ema_clk or posedge rst )

begin

if ( rst )

begin

StateIdle <= 1'b1;

StateRdSetup <= 1'b0;

StateRdStrobe <= 1'b0;

StateRdHold <= 1'b0;

StateWrSetup <= 1'b0;

StateWrStrobe <= 1'b0;

StateWrHold <= 1'b0;

end

else

begin

if ( StartRdSetup | StartRdStrobe | StartRdHold

| StartWrSetup | StartWrStrobe | StartWrHold )

StateIdle <= 1'b0;

else if ( StartIdle )

StateIdle <= 1'b1;

//read

if ( StartIdle | StartRdStrobe )

StateRdSetup <= 1'b0;

else if ( StartRdSetup )

StateRdSetup <= 1'b1;

if ( StartIdle | StartRdHold )

StateRdStrobe <= 1'b0;

else if ( StartRdStrobe )

StateRdStrobe <= 1'b1;

if ( StartIdle | StartRdSetup )

StateRdHold <= 1'b0;

else if ( StartRdHold )

StateRdHold <= 1'b1;

// write

if ( StartIdle | StartWrStrobe )

StateWrSetup <= 1'b0;

else if ( StartWrSetup )

StateWrSetup <= 1'b1;

if ( StartIdle | StartWrHold )

StateWrStrobe <= 1'b0;

else if ( StartWrStrobe )

StateWrStrobe <= 1'b1;

if ( StartIdle | StartWrSetup )

StateWrHold <= 1'b0;

else if ( StartWrHold )

StateWrHold <= 1'b1;

end

end

// clock counter

always @( posedge ema_clk or posedge rst )

begin

if ( rst )

clk_cnt <= 4'd0;

else if ( StartIdle | StartRdSetup | StartRdStrobe | StartRdHold

| StartWrSetup | StartWrStrobe | StartWrHold )

clk_cnt <= 4'd0;

else clk_cnt <= clk_cnt + 1'b1;

end

// control signals

assign dsl_oe_l = ~ ( StateRdStrobe | StateRdHold );

assign dsl_we_l = ~ ( StateWrStrobe );

assign dsl_ce_l = ~ ( StateRdSetup | StateRdStrobe | StateRdHold | StateWrSetup

| StateWrStrobe | StateWrHold );

assign dsl_8n16 = 1'b0;//1'b1

assign dsl_be_l = 2'b00;//16-bit

assign dsl_freeze = ( StateRdSetup | StateRdStrobe | StateRdHold );

assign bigend = 1'b1;

以下为另一状态形式程序,较直观,供参考: