【FPGA】LUT LATCH 傻傻分不清楚

0赞

LUT(Look-Up-Table):查找表。

LUT本质上就是一个RAM。它把数据事先写入RAM后,

每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

LATCH :就是锁存器。由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。

LUT和LATCH 他们的共同点是:均属于组合逻辑(和时钟没有半点关系)。

不同点是:LUT是FPGA最小单元的组成结构,而LATCH不是。

说道LATCH就不得不提到FF,FF(Flip Flop):触发器。

那么DFF就是,众所周知的D类触发器。它是边沿触发的,归为时序逻辑。

他和reg又有着什么关系呢?reg就是由DFF组成的。一个8位的寄存器,就是用了8个同步的D触发器。

一般一个FPGA最小单元就会包含多个LUT和多个REG,且REG的个数多于LUT。(这个以后再具体分析)

关系都找出来了,我们来做些实验,看看下列代码都能综合出什么东西:

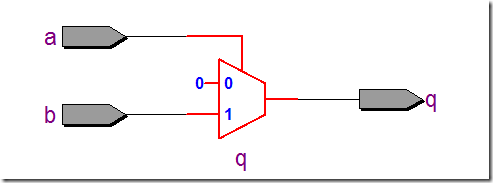

实验1:

module testlatch ( input a, input b, output reg q ); always @(a or b) if(a == 1'b1) q = b; endmodule

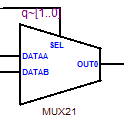

实验2:

module testlatch ( input a, input b, output reg q ); always @(a or b) if(a == 1'b1) q = b; else q = a; endmodule

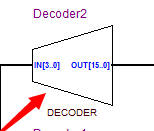

实验3:

module testlatch ( input CLK, input a, input b, output reg q ); always @(posedge CLK) if(a == 1'b1) q = b; endmodule

总结:

1、always (*)或者 assign 综合出的就是LUT构建的东西,可认为就是LUT。

2、在always (*)的情况下,如果if 或者cace 不完整的话,会综合出latch,导致不稳定。

3、在always (posedge CLK)的情况下,综合出的是reg,即使if,或者case不完整,也不会综合出latch。

4、不要用latch作为模块名,会报错,这个名字已经被Quartus占用了。

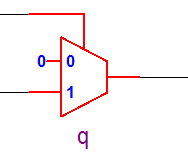

大家可能会说,并没有看到LUT,我们知道LUT就是查找表,去technology Map Viewer,去看看:

就知道RTL那些 “梯形的选择器” ,其实就是由LUT构成的!!

梯形选择器,类似于:

一句话点题:

万能查表法再加上寄存器就保证了快速运算逻辑,这就是FPGA!

技术讨论欢迎加群~~电子技术协会 362584474