MiZ702学习笔记3——熟悉Vivado开发流程从PL开始

0赞废话不说,直接进入主题~~~

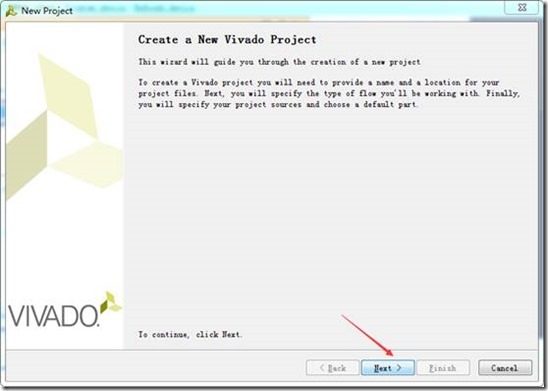

1、选择菜单栏File->New Project:

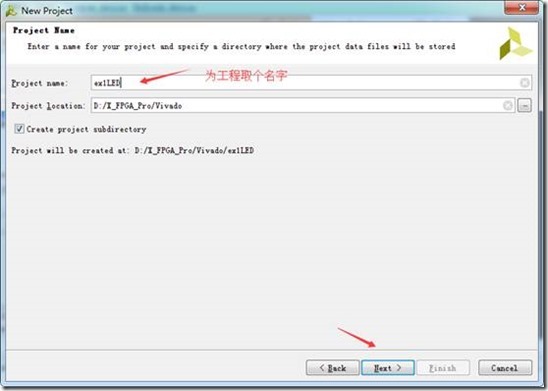

2、为工程取名

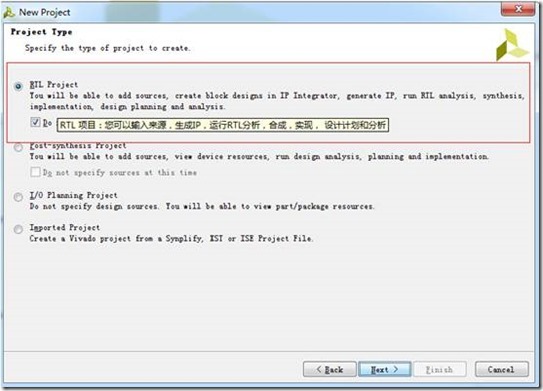

3、选择RTL项目

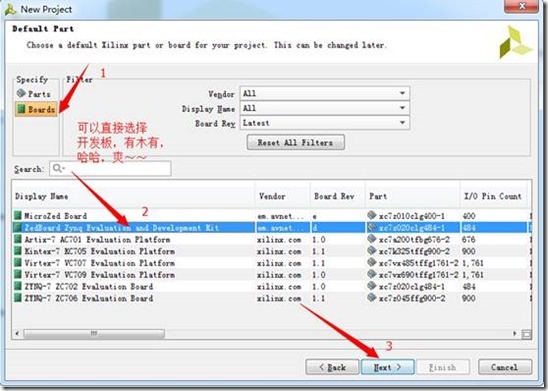

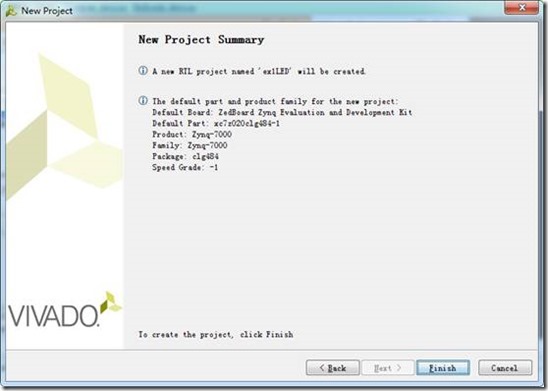

4、由于MiZ702和zed高度兼容,我们不妨试试直接选择ZedBoard,当然这仅仅是个尝试哈哈,如果是比较严谨的项目,还是跟新芯片型号选择。

5、完成

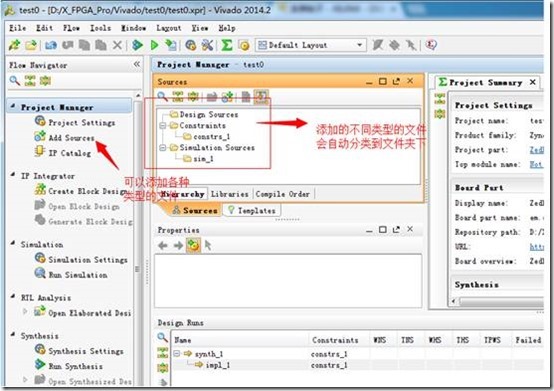

工程就创建好了,我们来看下主界面:

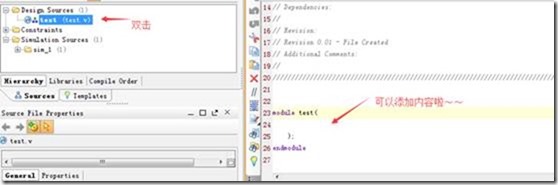

接下来,我们就先添加一个.V文件:

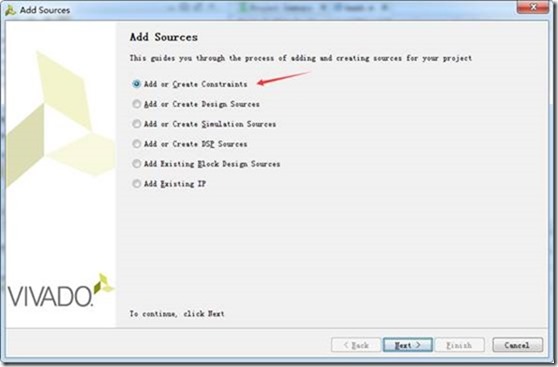

1、点击Add Source

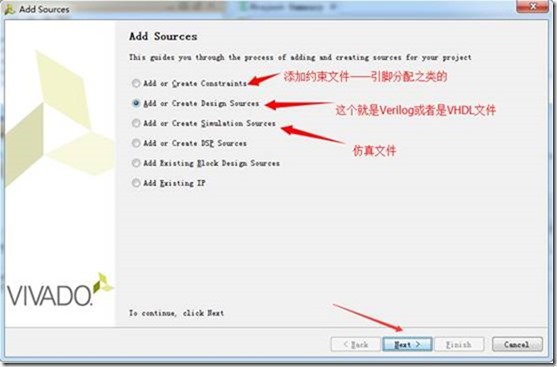

2、我们选择第二项,点击Next

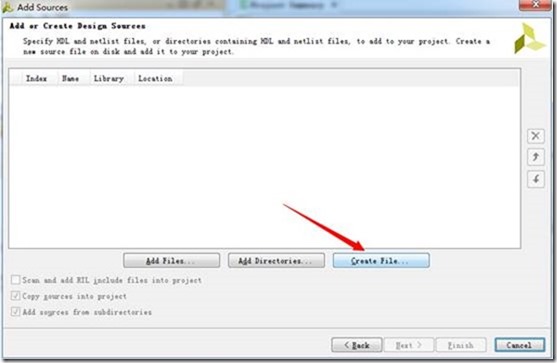

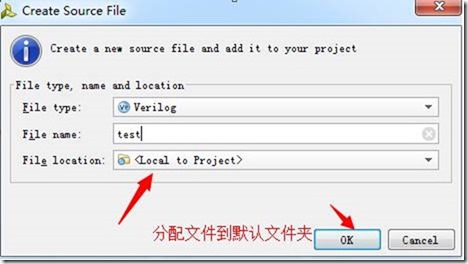

3、

4、填写文件名,默认文件类型是Verilog

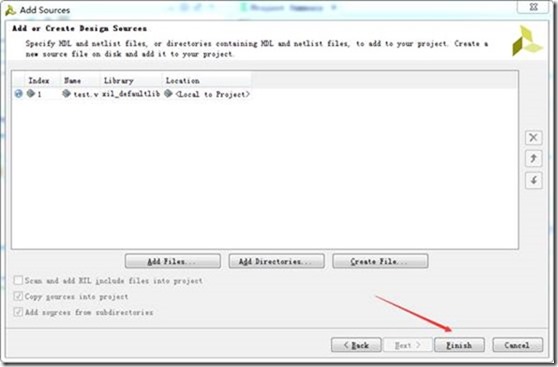

5、

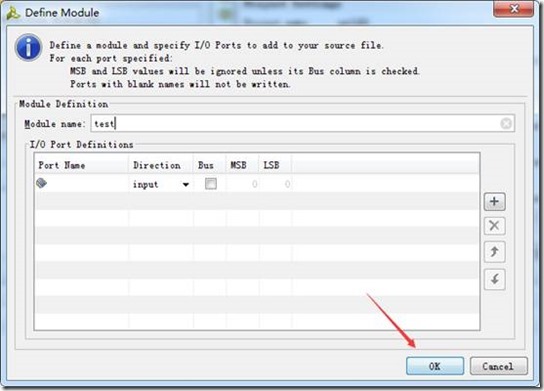

6、

7、直接Yes,完成

8、可以向我们的程序里添加内容啦

9、添加内容如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2015/06/20 06:01:43

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module test(

input CLK,

input RSTn,

output reg [7:0]LED

);

reg [31:0]C0;

always @(posedge CLK or negedge RSTn)

if(!RSTn)

begin

LED <= 8'b0000_0001;

C0 <= 32'h0;

end

else

begin

if(C0 == 32'd50_000_000)

begin

C0 <= 32'h0;

if(LED == 8'b1000_0000)

LED <= 8'b0000_0001;

else LED <= LED << 1;

end

else begin C0 <= C0 + 1'b1; LED <= LED; end

end

endmodule

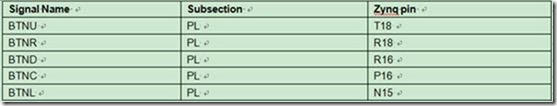

这样一个简单的流水灯程序就完成了,我们开始分别引脚,这是可以打开我们提供的《硬件使用手册》,来分配LED引脚,非常的方便。

1、系统时钟

MiZ702 核心板上具备一颗33.333MHZ的时钟输入到PS部分,底板具备一颗100MH时钟输入到PL部分Y9 管脚。

MiZ702 核心板上具备一颗33.333MHZ的时钟输入到PS部分,底板具备一颗100MH时钟输入到PL部分Y9 管脚。

2、系统复位

这部分是FPGA部分的逻辑资源复位,此管脚接到MiZ702核心板上SW1脚

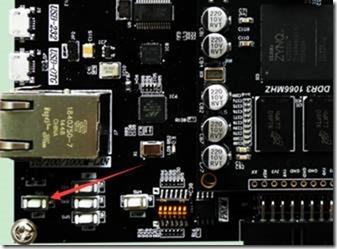

核心板上,不需要分配,我直接把复位引脚分配到底板的BTNL吧,引脚N15

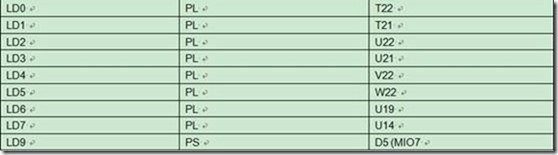

3、LED分配

首先新建一个约束文件——XDC,过程和新建.V文件一样,就不重复了:

具体引脚分配如下

时钟分配如下:

set_property PACKAGE_PIN Y9 [get_ports {CLK}]

set_property IOSTANDARD LVCMOS33 [get_ports {CLK}]

这两句缺一不可~~

第一句不用我说了,第二句是规定IO是什么电平标准: LVCMOS 3.3V,没错就是它~~

复位引脚分配:

set_property PACKAGE_PIN N15 [get_ports {RSTn}]s

set_property IOSTANDARD LVCMOS18 [get_ports {RSTn}]

之后就就是LED的分配:

set_property PACKAGE_PIN T22 [get_ports {LED[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[0]}]

set_property PACKAGE_PIN T21 [get_ports {LED[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[1]}]

set_property PACKAGE_PIN U22 [get_ports {LED[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[2]}]

set_property PACKAGE_PIN U21 [get_ports {LED[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[3]}]

set_property PACKAGE_PIN V22 [get_ports {LED[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[5]}]

set_property PACKAGE_PIN W22 [get_ports {LED[5]}]

set_property PACKAGE_PIN U19 [get_ports {LED[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[7]}]

set_property PACKAGE_PIN U14 [get_ports {LED[7]}]

好了开始编译吧,目的就是可供下载的bit文件,直接点击如下图所示:

这里可以看到具体进度,不过感觉进度条什么的,都是骗人的,呵呵~~

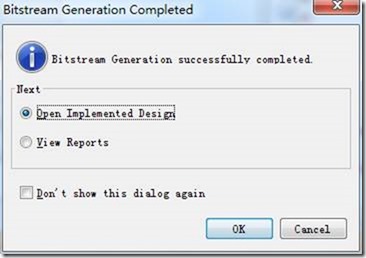

好了,编译完成,具体什么东西就不查看了,点击取消:

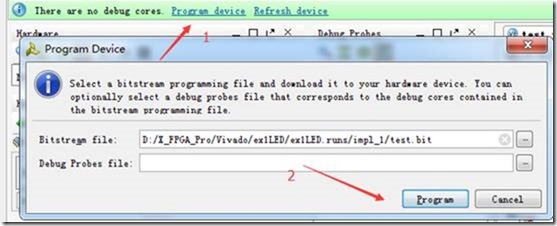

接下是下载

最后,流水灯已经奔跑起来!!!

这里,祝大家端午快乐。