Verilog的信号强度学习

0赞现在在cadence中用NC仿真数字电路的时候,遇到了信号强度的问题,就研究了以下。原来verilog中是可以将多个输出接在一起的,但是要为输出指定信号的强度。

强度值是用来解决数字电路中不同强度的驱动源之间的赋值冲突。

我们知道设计数字电路时候,特别是用MOS管设计时,有时候是需要将多个输出接在一起的,这个时候输出由哪个输入决定,就要看电路的MOS管的参数,谁的强度大,就输出哪一个的。

Verilog中:

如果两个具有不同强度的信号驱动同一个线网,则竞争结果值为高强度信号的值。

如果两个强度相同的信号之间发生竞争,则结果为不确定值。

下面就进行测试。

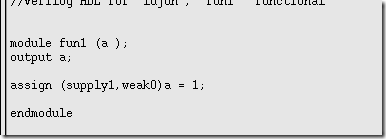

首先写两个简单的模块,两个模块都是输出,然后输出接在一起。第一个模块是输出强1,弱0.第二个模块输出弱1,强0。

强度定义是在信号的前面的()中定义,注意()中需要两个值,一个指定输出高电平的强弱,一个指定输出低电平的强弱。

第一个模块,指定输出a的高电平的强度是supply1,就是最高。低电平的强度是week0,比较弱。

第二个模块,指定输出a的高电平和低电平强度都是week。

那么可以知道,输出肯定是1,因为第一个模块是输出高强度的1.

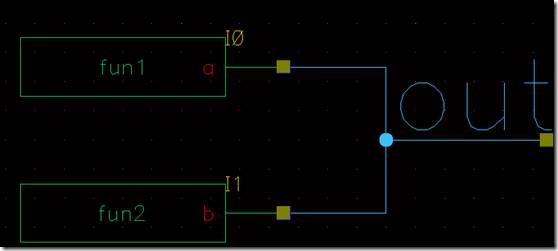

在顶层连接两个模块。

仿真结果

输出是高电平。

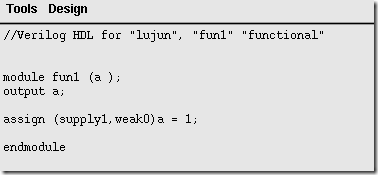

改一改模块的程序:

让b输出0的强度也是supply。。

那么这个时候输出就是未定态X了。

仿真结果也可以看得出来。

对于表中的强度等级,后面标注为驱动的,可以按照上面的方法进行仿真。不知道存储类型是用来干嘛的,按照上面的写法,会报语法错误。

可以看出,verilog还是比较强大的。

![clip_image001[1] clip_image001[1]](http://files.chinaaet.com/images/blog/2015/03/23/2930194853628.png)