Vivado封装自定义IP

0赞Vivado可以将自己的verilog代码设计封装成IP,然后在设计中调用该ip.ip还可以配置参数。所用软件为2014.4

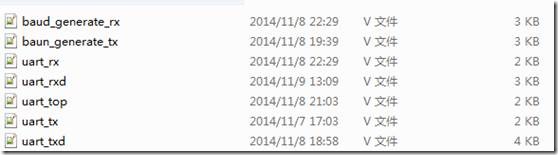

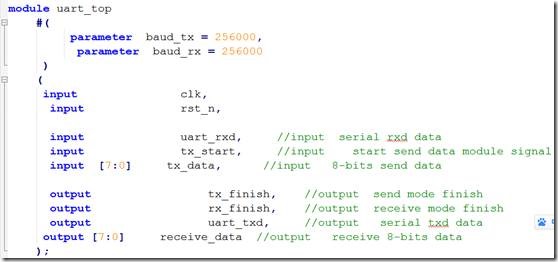

下面以我之前写的一个串口程序为例。

将代码拷贝到一个目录下,该目录不能有中文和目录。

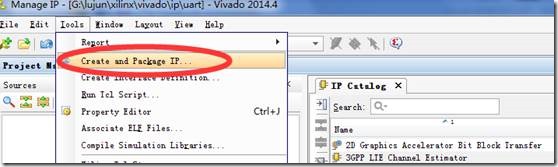

然后打开vivado软件。

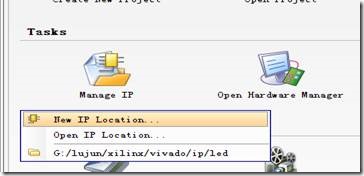

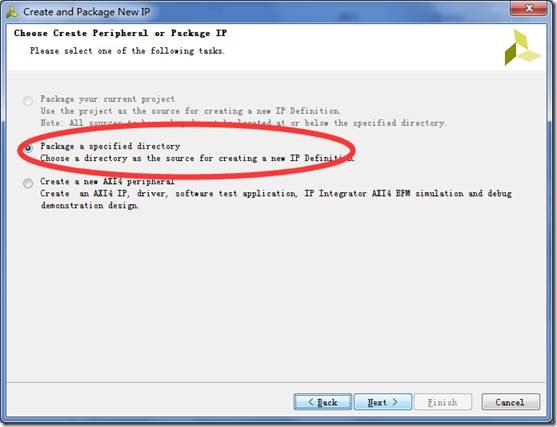

选择创建和封装IP。

因为是要封装IP,选择第二个

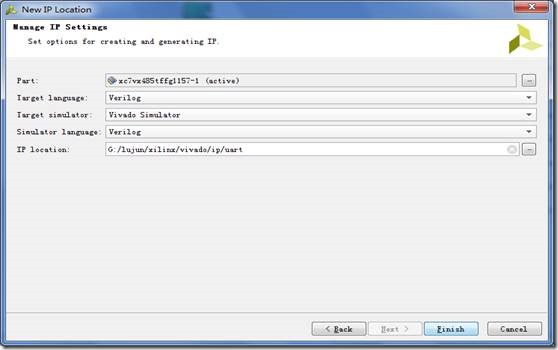

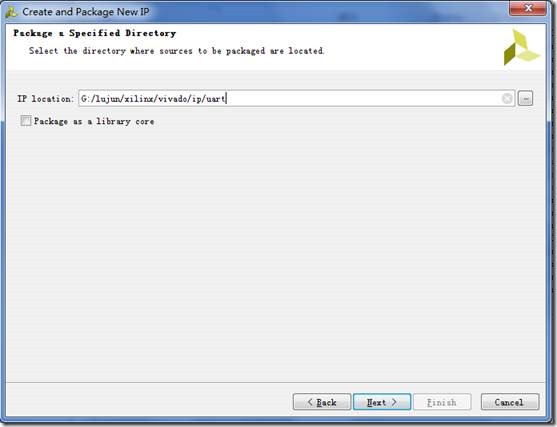

为ip指定一个路径。

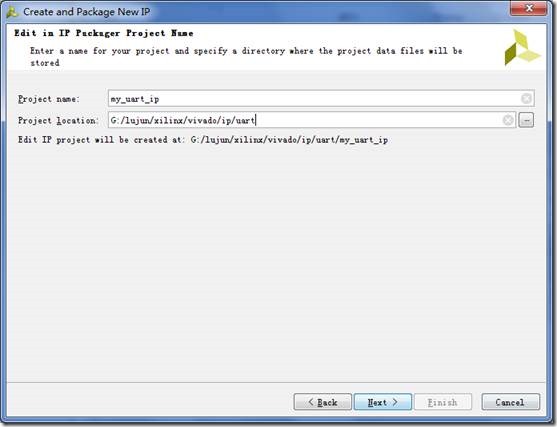

为IP设定工程名和工程路径。

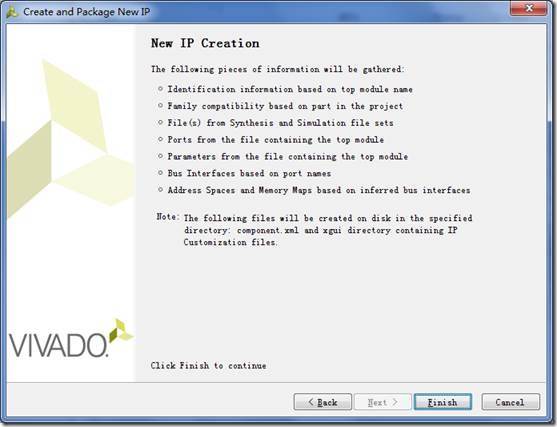

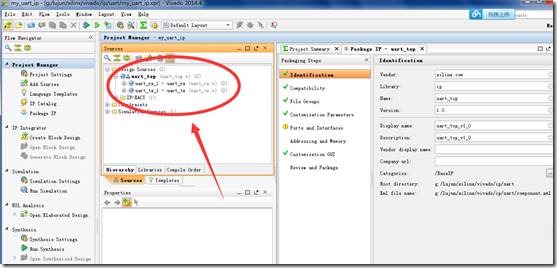

这样,就创建好了IP工程。可以看到软件会自动导入设计,并将顶层代码给设置成顶层。

右边部分就是设置IP。

第一个是配置一些IP信息,可以在这里填入一些信息。

在categories,可以更改IP的类型,这样的话,方便以后查找。

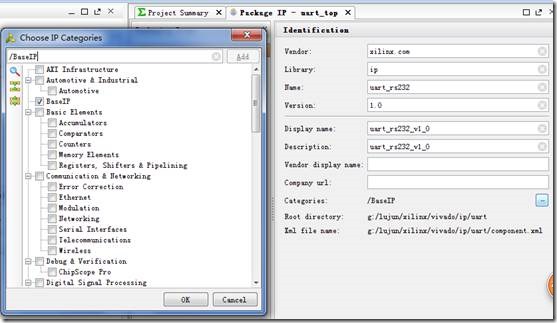

第二项是配置IP在哪些器件上可以用。

可以添加器件。

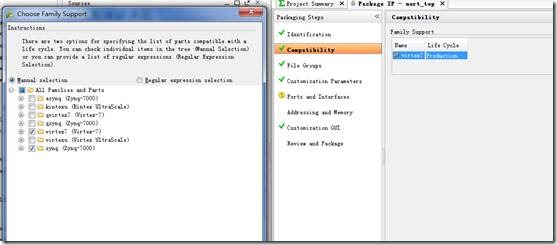

第三个是代码的一些文件

包含综合和仿真。

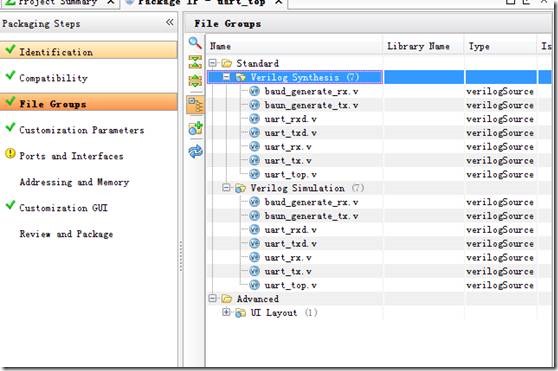

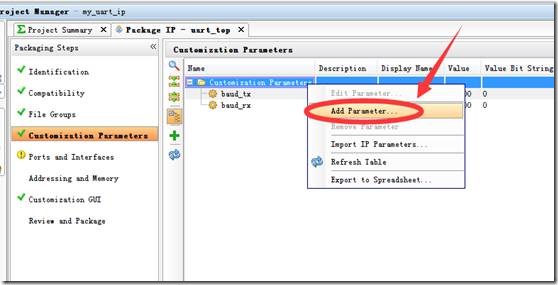

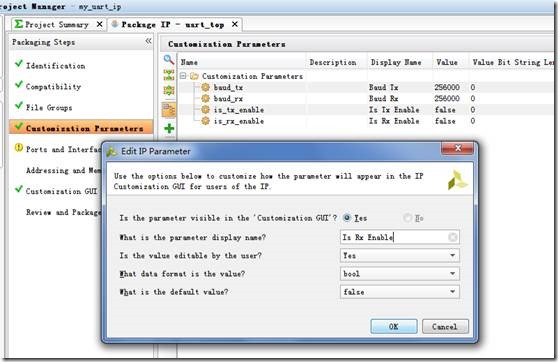

第四个是定义IP的参数。

在顶层代码中,使用parameter定义了两个参数,所以软件会默认把这两个参数给加进参数列表中。

在这里,我们填加两个信号,

is_tx_enable: 发送使能

is_rx_enable: 接收使能

两个信号是用来选择发送和接收是否使能的。因为有可能我们只会用到串口的一个功能。

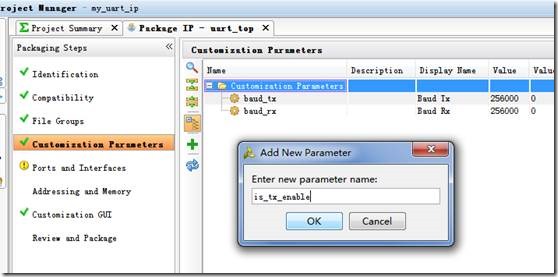

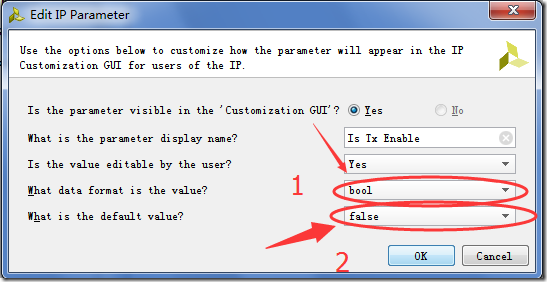

然后进入参数设置列表。

这里有几个设置,第一个设置是设置参数的类型,第二个是设置参数的默认值。这里因为是一个使能信号,所以设定为bool型,默认是false。

然后再添加ix_rx_enable信号。

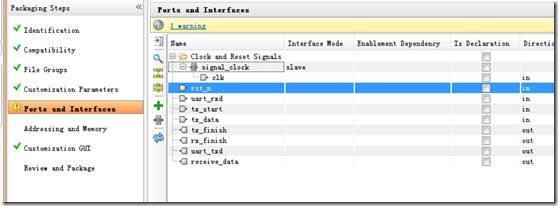

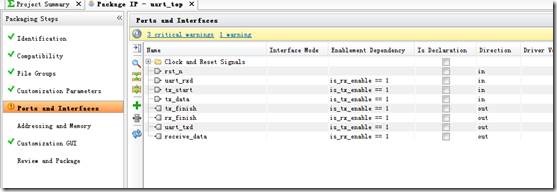

下面一个是设置端口的。如图,软件很自动的把顶层的信号给设置成端口。在这里,是可以设置这些IO端口是使能还是不使能的,这个时候就需要用到在上面定义的参数了。

在参数列表中,定义了一个is_tx_enable信号,这个信号有效的时候,使能发送,那么发送的端口就有效,否则发送的端口就无效。

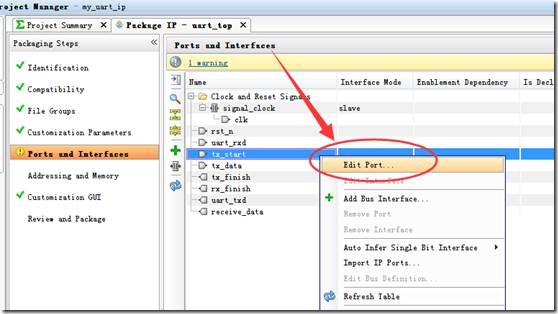

以后设置发送的一些端口。

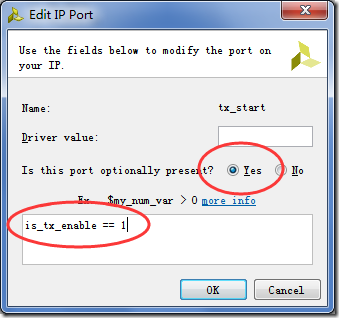

在端口选项选择yes,表示端口是可以配置的。然后再下面的框中填入表达式

Is_tx_enable == 1 。说明档参数is_tx_enable为1的时候,端口是有效的。

依次设置其他的一些管脚。

对发送和接收的部分都设置为参数使能。

下一个是地址和内存配置,这个目前还不知道有什么用。这里也不需要,跳过。

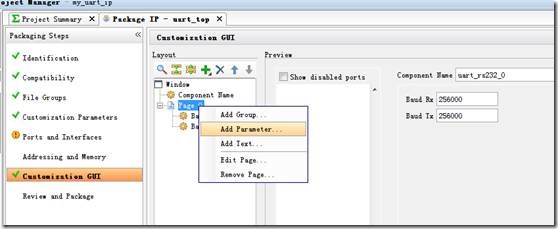

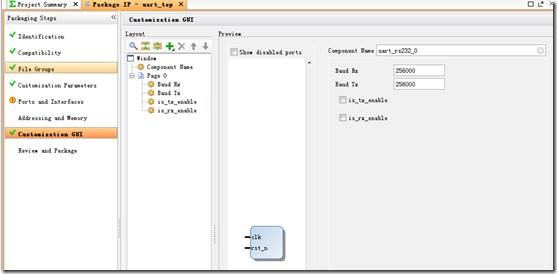

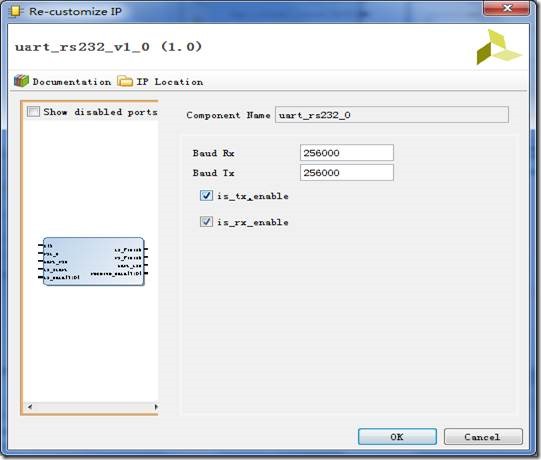

最后一个就是IP的界面配置设置。当我们用IP的时候,会出现一个图形化界面,来对IP进行配置,这个就是实现这样的功能的。

下面是默认的参数,可以看到这里默认有两个参数,视图里面只有时钟和复位管脚,因为我们定义了两个使能参数对发送和接收使能管脚配置,而参数默认为是false的,所以发送和接收的管脚都没有使能。

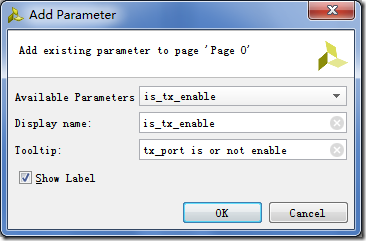

添加参数

这里可用的参数就是我们之前在参数配置界面添加的那两个,将两个都加进来。

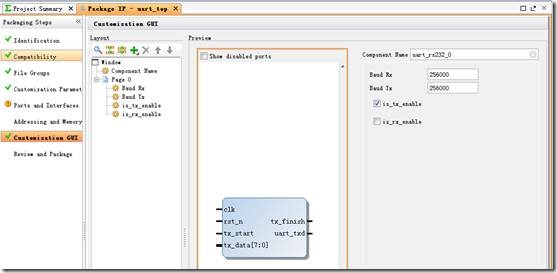

这个时候参数那边就多了两个了。我们使能其中一个,is_tx_enable。

可以在视图看到发送的管脚加入了进来。

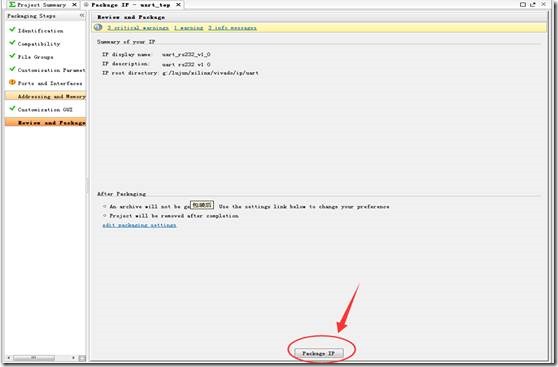

最后对封装的IP进行打包就可以了。

这样,就对我们的IP给封装好了。。。然后就直接在使用中调用就可以了。

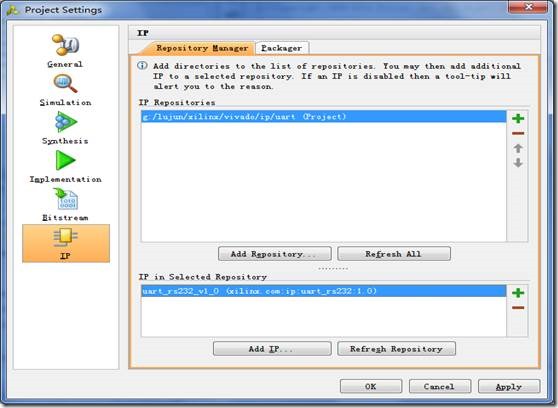

首先要在工程设置中加入IP的位置。

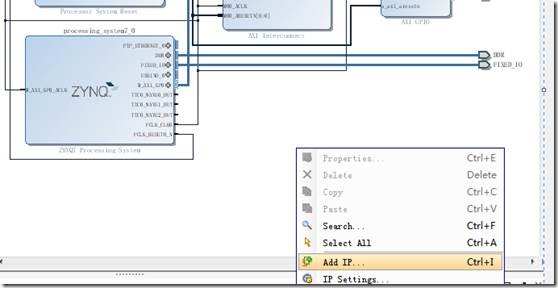

然后在设计中直接添加IP就可以了。

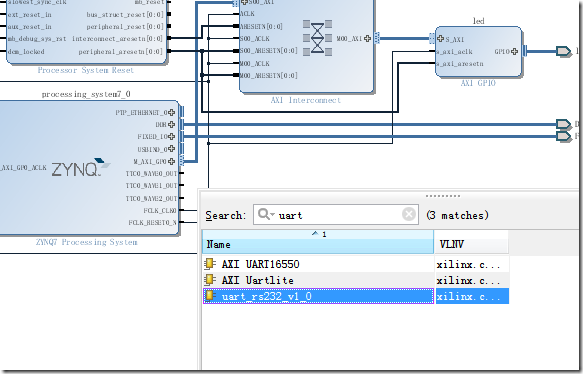

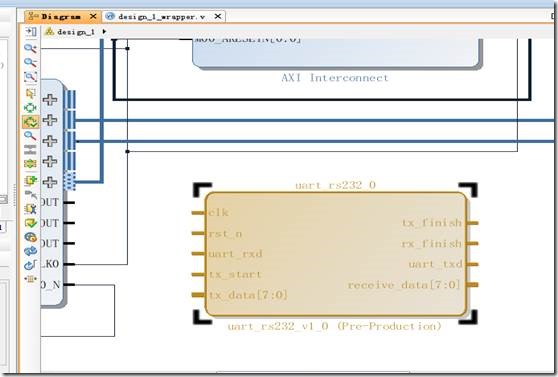

选择我们封装的IP

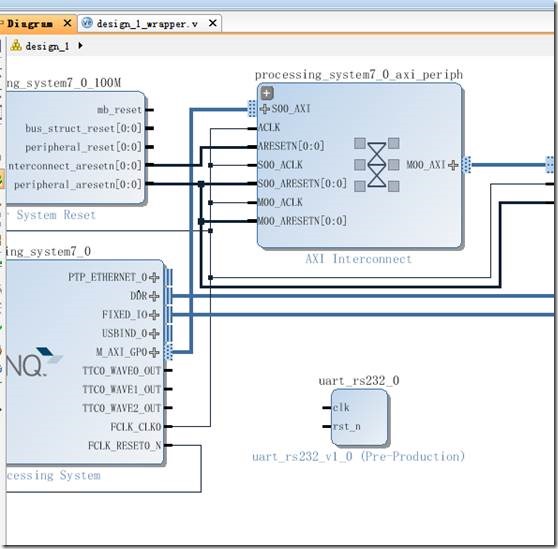

就出现了

然后双击对IP进行配置

这样,一个IP就调用配置了。

接下来就对IP进行连线,和生成外部管脚,并对管脚加约束就可以了。

可以看到,vivado软件比ISE在IP方面要好用多了。而且使用也比较简单。