第二章 SOC DDRMemory

1赞本教程是基于南京米联电子科技有限公司 MiS603 Spartan6开发板进行,软件采用ISE14.7。本系列教程就是带领大家学习XILINX EDK开发板工具以及SDK下的编程。本教程官方论坛:www.osrc.cn

在上一章节中笔者详细讲解了EDK工具和SDK的开发流程。本章将对板载的DDR3内存做一个测试。

在开始实验前,请确保你的电脑已经安装好ISE14.7,本教程省略最基本的新建工程的具体细节。

1.1添加DDR内存工作时钟

Step1:复制上一个例子的工程,并将文件夹名字改为DDRMemory

Step2:双击工程文件MiS603_SOC.xise

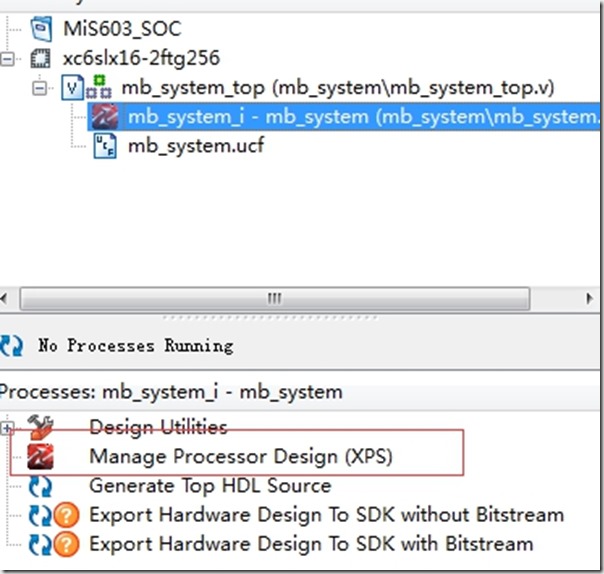

Step3:在ISE下启动XPS

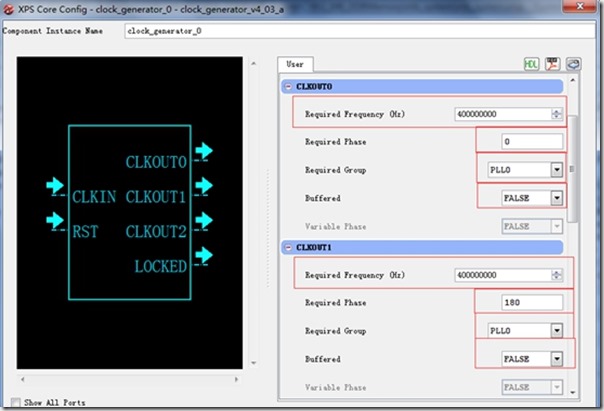

Step4:修改时钟,设置DDR工作时钟和更改系统时钟

DDR3的运行时钟,设置为核心频率400MHZ

系统时钟设置为100MHZ并且改为从时钟2输出带缓冲

Step5:时钟管理部分对时钟命名

1.2添加AXI interconnect 总线IPCORE

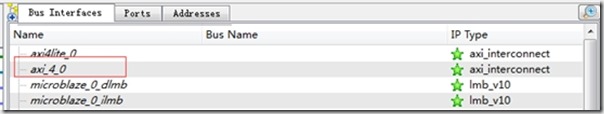

Step1:添加AXI interconnect 总线IPCORE 如图

Step2:修改名字为axi_4_0

Step3:设置端口信号的时钟和复位

1.3修改microbalze cpu配置

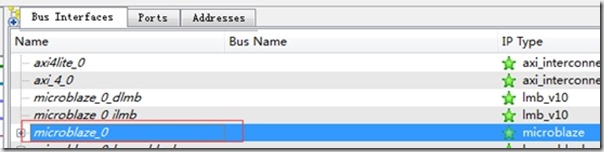

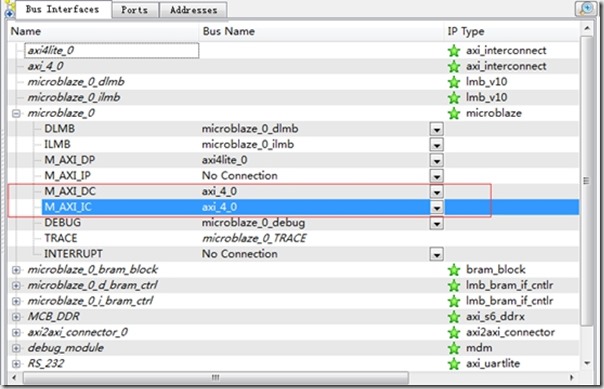

Step1:双击microblaze_0 IP CORE对microblaze CPU配置

Step2:设置如下图,启动调试功能和cache功能,之后单击next

Step3:设置指令支持的功能

Step4:设置调试下需要的断点,和监控点之后单击NEXT

Step5:配置cache然后单击Next

Step6:单击OK完成配置

Step7:将cache通过axi_4_0连接总线

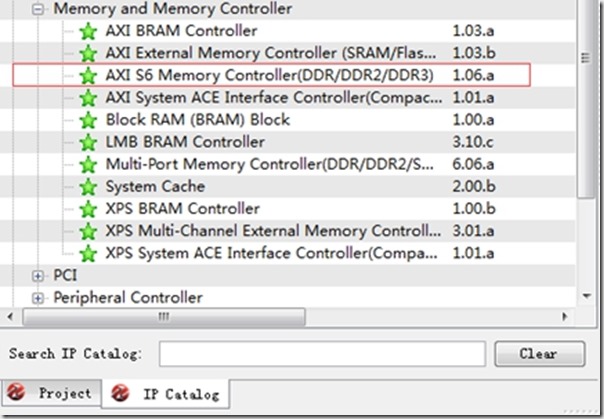

1.4添加内存控制器 IPCORE

Step1:启动完成后添加MCB硬核控制器IP CORE

Step2:配置MCB控制,由于本开发的DDR3内存在bank3上,因此设置如下图后单击NEXT

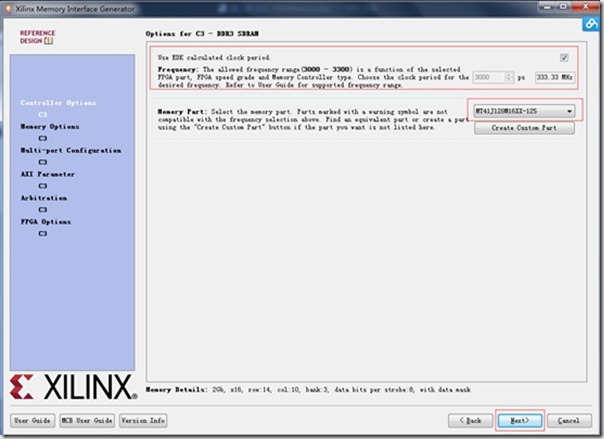

Step3:设置DDR3的工作频率和支持的类型(可以是兼容型号)

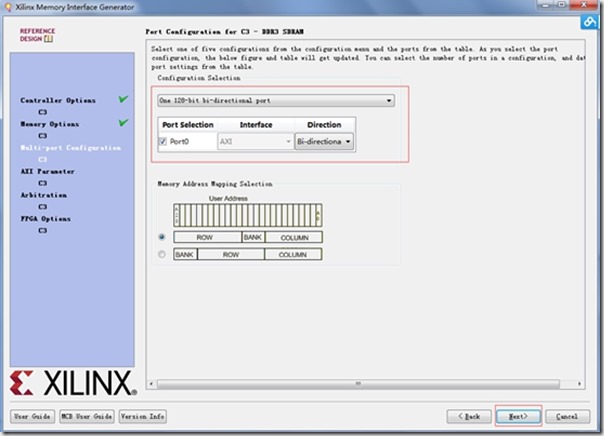

Step4:本页不设置直接单击Next

Step5:设置MCB控制器位宽之后单击Next

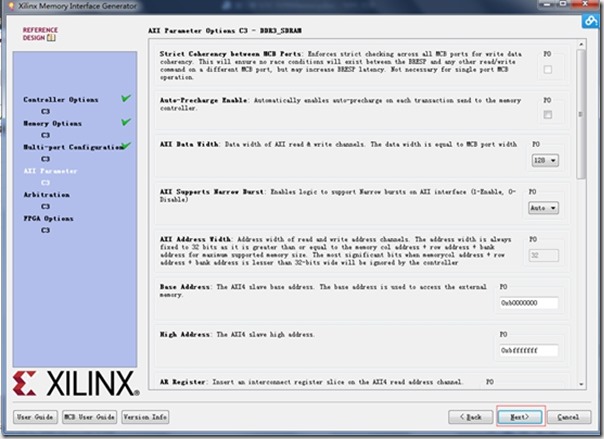

Step6:单击NEXT

Step7:单击NEXT

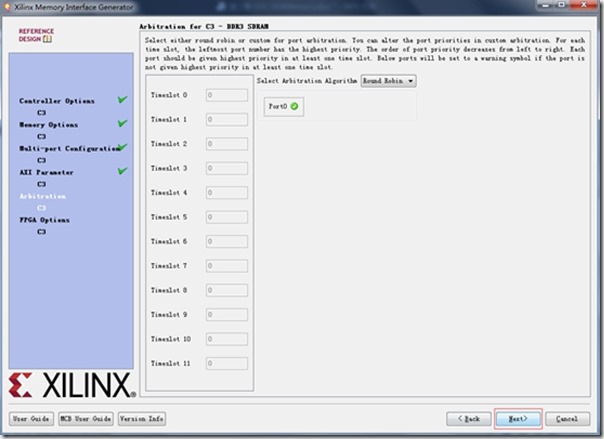

Step8:设置如下图,之后单击Finish

Step9:修改IP名字为MCB_DDR

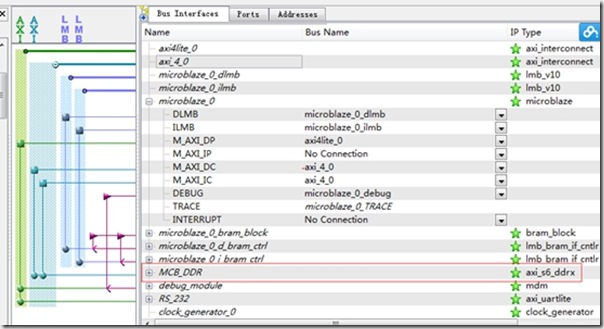

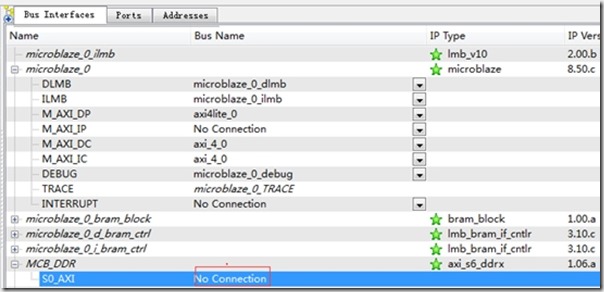

Step10:设置MCB_DDR的总线连接,单击下图框选区域

Step11:设置cache到DDR内存控制的连接,之后单击OK

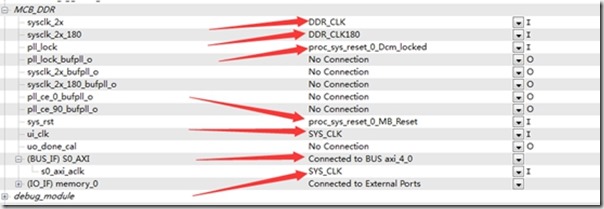

Step12:设置内存控制器DDR的时钟

1.5编译工程

Step1:双击下图红色方框内,重新产生顶层文件

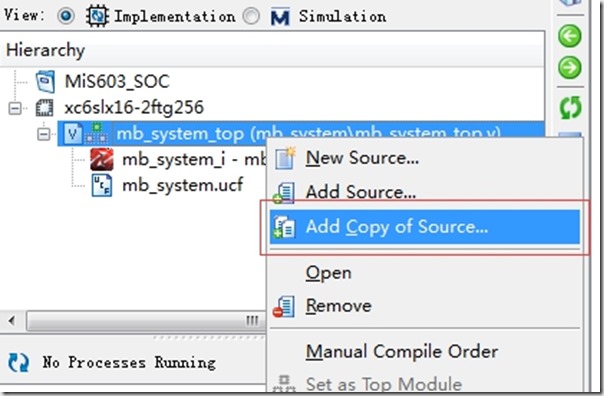

Step2:右击选择添加拷贝的UCF文件

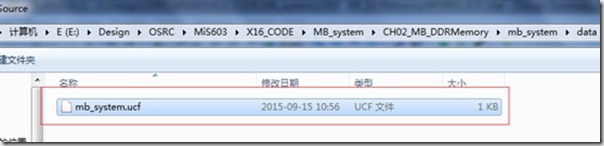

Step3:拷贝UCF文件

Step4:双击下图框选位置,进行编译

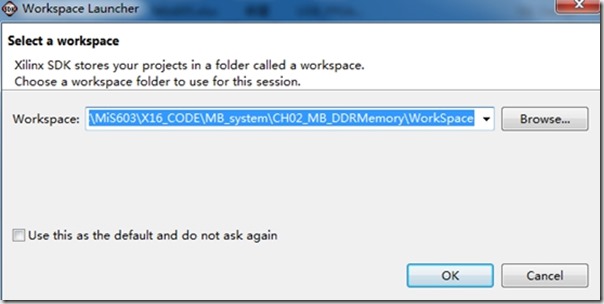

Step5:修改SDK工程的路径(读者自己指定文件相对路径)

1.6 SDK开发

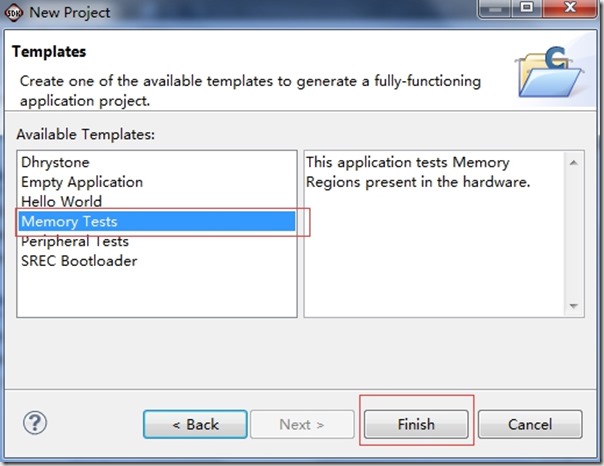

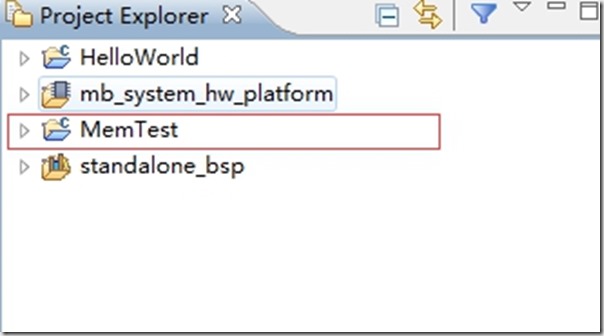

Step1:新建工程为MemTest

Step4:采用系统自带的Memory Tess模块例子

Step5:C工程,默认会采用自动编译,当有程序文件改动,并且保存后就会编译

1.7下载及调试

Step1:准备好开发板,插上下载器,记住USB线要插上,并且通电,由于拍摄时间问题,本没有插上。

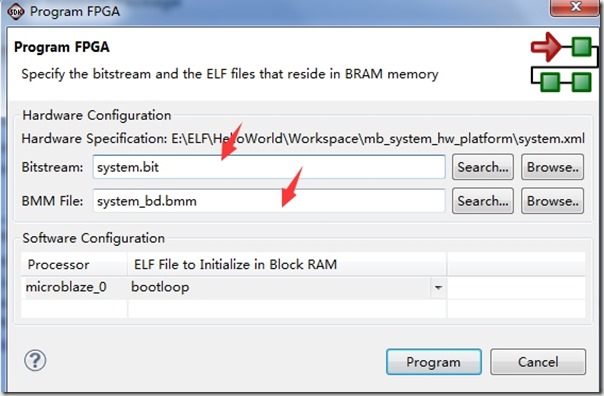

Step2:下载SOC硬件电路到FPGA

35、ISE14.7会自动识别需要下载的文件

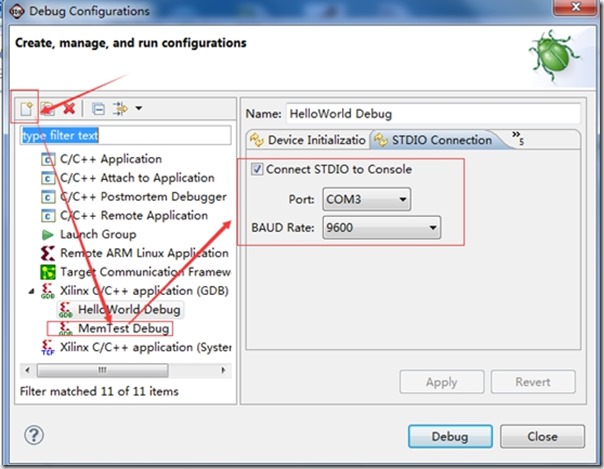

Step3:右击工程

->Debug AS

->DebugConfigurations

Step4:新建一个测试文件,配置串口波特率9600 单击Apply 再单击 Debug

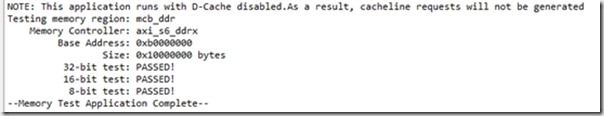

Step5:测试结果:输出

1.8本章小结

本章讲解的MCB 硬核控制器IP 在SOC开发下如何使用的例子,当程序稍微有点大的时候,都需要把程序放在大的内存中运行,DDR是一种廉价高速的内存芯片,xilinx FPGA spartan6非常方便地提供了MCB控制器的IP,使用起来非常方便。通过学习本章的例子,可以为以后使用打好基础。