zynq中断学习

0赞Zynq的PS是基于ARM架构,使用两个ARM Cortex A9处理器和GIC pl390中断控制器。

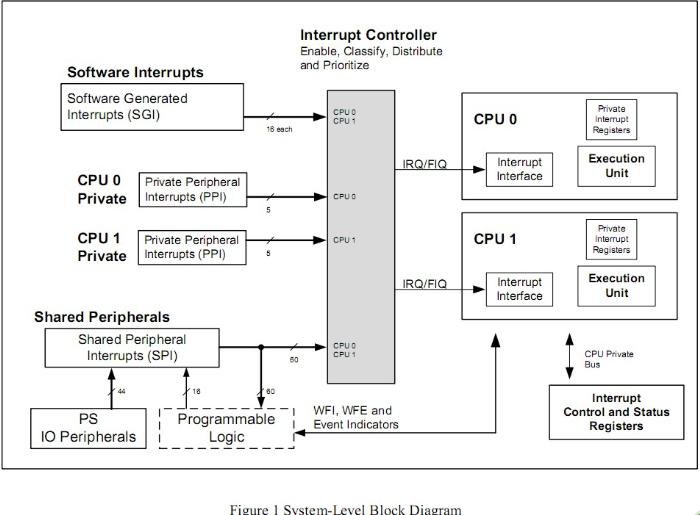

系统中断框图如下:

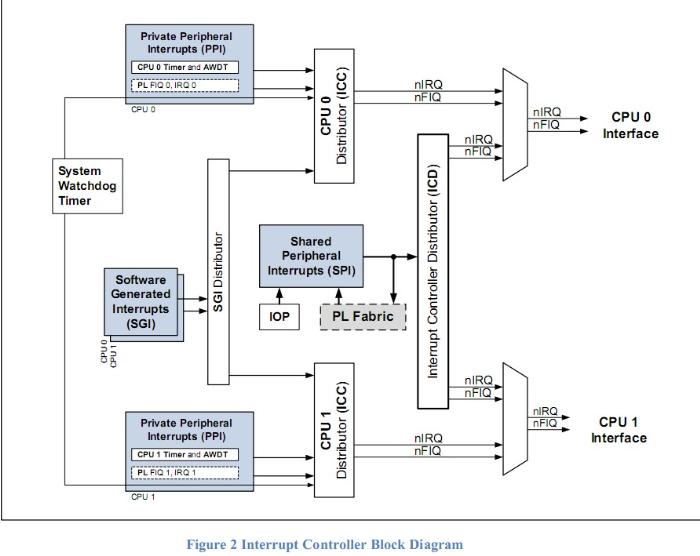

Interrupt Controller(中断控制器)框图如下:

中断详细分为SGI(Software Generated Interrupts)软件中断,PPI(Private Peripheral Interrupts)私有外设中断,SPI(Shared Peripheral Interrupts)共享外设中断。

1. SGI软件中断

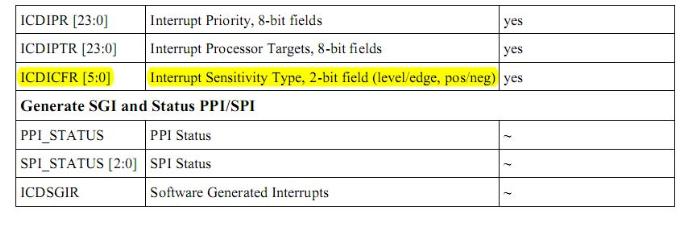

存在16个软件产生的中断,通过向ICDSGIR寄存器写入SGI中断号,以及指定目标CPU,来产生一个软件中断,通过读ICCIAR寄存器或者向ICDICPR寄存器相应的比特位写1,可以清楚中断。所有的SGI为边沿触发。

2. PPI私有外设中断

每个CPU连接一个私有的共享5个外设中断,素有中断的敏感类型是固定的,不能改变,UPI全局定时器,nFIQ,CPU私有定时器,AWDT,nIRQ。

3. SPI共享外设中断。

由PS和PL上的各种I/O控制器和存储器控制器产生,这些中断信号会被路由到CPU。PS的外设产生的SPI中断也会路由到PL上。默认地,所有共享外设中断类型在复位时是高电平,然后软件使用的ICDICFR2和ICDICFR5寄存器编程中断32,33和92为上升沿敏感。

寄存器表

主要用到的中断函数有:

XScuGic_LookupConfig 中断设置查找

XScuGic_CfgInitialize GIC初始化

XScuGic_SetPriorityTriggerType 设置中断优先级及中断触发方式

XScuGic_Connect 设置中断服务程序入口地址

XScuGic_Enable GIC允许

XGpio_InterruptGlobalEnable GPIO全局中断允许

XGpio_InterruptEnable 相应GPIO中断允许

Xil_ExceptionInit 异常处理函数

Xil_ExceptionRegisterHandler

Xil_ExceptionEnable

实验部分在下一篇博客中叙述。