【读书笔记】inout口modelsim仿真

0赞拿到CB书好久了,直到现在才开始写自己的心得。

看到书中CB的经历,就像当初看到郭天祥经历一样,令人十分振奋。

书中也介绍了软件的安装和一些警告的消除,这让我觉得CB是真的在告诉我们怎么去学好FPGA。

然而,CB一直在强调代码风格和设计是基于测试的,也就是DUT,每一个module都在严格的仿真!!!似乎我找到自己为什么那么菜的原因了。

好吧,那就这样做了,再不直接上板了,这都做不到那还玩个屁啊!

就从inout口仿真开始吧,这个之前还真没有仿真过。。。。

Verilog实现:

实现说明:z为0是,inout 是做输出用,输出的数据时din(输入input)

z为1 是,inout 是做输入用,输入的数据给dout(输出output)

module test_inout(clk,z,din,dinout,dout); input clk; // input z; //control signal input [15:0]din; //input signal inout [15:0]dinout; // bi_inout output [15:0]dout; //output signal reg [15:0]dout; reg [15:0]din_t; assign dinout=(!z)?din_t:16'bz; always @(posedge clk) begin if(!z) din_t<=din; else dout<=dinout; end endmodule

不得不说,一开始还真是各种错误,网上搜解决方法,终于实现了:

首先我利用的是生成的testbench模板,生成的模板帮我们解决了很多问题。生成的inout口是wire型变量,这里添加了一个reg型的treg_dinout,用来表征inout的输入,也就是当treg_dinout赋具体的数值时,这个时候inout是做输入用的,即dout的数值就是treg_dinout的数值,当treg_dinout为16‘bz时,也就是断开了,不做输入,那就是inout做输出了,dinout输出的就是din的数据了,下面看testbench和modelsim仿真了。

Testbench:

// Copyright (C) 1991-2011 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

// *****************************************************************************

// This file contains a Verilog test bench template that is freely editable to

// suit user's needs .Comments are provided in each section to help the user

// fill out necessary details.

// *****************************************************************************

// Generated on "11/10/2014 15:19:03"

// Verilog Test Bench template for design : test_inout

//

// Simulation tool : ModelSim-Altera (Verilog)

//

`timescale 1 ns/ 1 ps

module test_inout_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg clk;

reg [15:0] din;

reg [15:0] treg_dinout;

reg z;

// wires

wire [15:0] dinout;

wire [15:0] dout;

integer i;

// assign statements (if any)

assign dinout = treg_dinout;

test_inout i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.din(din),

.dinout(dinout),

.dout(dout),

.z(z)

);

initial

begin

// code that executes only once

// insert code here --> begin

clk=0;

din=0;

z=1; //input

treg_dinout=20;

#200 for(i=0;i<10;i=i+1)

#20 treg_dinout=treg_dinout-1;

z=0; //output

treg_dinout=16'bz;

// --> end

$display("Running testbench");

end

always #10 clk=~clk;

always #20 din=din+1;

endmodule

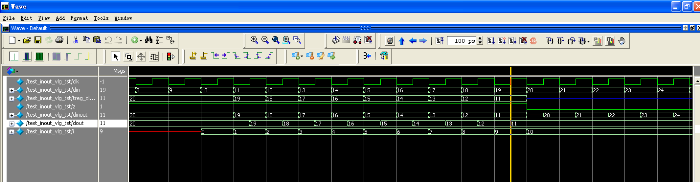

z=1,inout做输入,dout的值就是treg_dinout(也就是dinout)的值,

z=0,inout做输出,dinout的值就是din的值

在testbench中,inout的信号定义成wire型,input是reg型,output是wire型。inout需要定义一个reg型变量如上面,如上图reg [15:0] treg_dinout;并且assign dinout = treg_dinout;然后,

当需要inout做输入时,直接给treg_dinout赋值就可以了。

当需要inout做输出时,直接给treg_dinout=16‘bz,这样就可以实现了。

另外还一种方法就是使用force和release语句,但这种方法不能准确反映双向端口的信号变化,这一种方法就不试了。