【读书笔记】CB代码风格和modelsim仿真

0赞像借着新电脑之机,认真搞搞FPGA,没想到一个小小的仿真工程也让我栽了半小时的跟头(见后面)。

读书心得

看完了前5章,自己新买的电脑各种环境在11.15号也搭建完毕。记录下自己觉得有收获的地方

1. 按照CB工程文件目录,可以对工程文件有很好的一个管理,最先想到的就是在modelsim中对每个v文件仿真都是一个仿真工程,在sim文件夹下建立各个仿真工程的目录,管理起来相当容易,以后都应采取这种文件结构。

FPGA工程目录:dev ,core,src,sim,doc

其中dev 一般是工程建立后不用再管,保存的是工程设置,脚本等

Core需要用户将quartus II 的IP核保存在这个目录

Src是用户设计的verilog源文件

Sim主要存放的是modelsim仿真测试工程,里面继续分层,因为有很多个测试子工程

Dev是关于设计的档案,参考等信息

2. HDL代码风格设计

文件头编写:包括版本之类的信息

Module列表编写规范

Always块编写规范

Module例化规范

在以后的设计中,尽量形成这种良好的代码风格

3. Testbench设计

也需有编写的风格,本人以前的仿真中,都是用软件生成一个testbench的模板,然后添加时钟,复位,激励等,至此,抛弃软件生成模板,这时候,编写一般的task,如时钟和复位。这样也方便代码的可读和移植

4. 仿真时不错的地方

这里才用的直接在modesim下仿真,即在modelsim下建立仿真工程,和我之前的在quartusII下调用modelsim有不同,文件可以用notepad ++独立编写。然后在modelsim下进行编译和仿真。在仿真有下面几点感觉不错。

A. 在不退出simulation的前提下进行代码修正,修正后,compile-》Restart(不是重启modelsim)

B. 手动添加仿真时间,在Transcript中run 1000ns等

C. 每一次仿真时都要添加信号,会显得麻烦,做法是保存波形wave.do,然后下次打开的时候load就可以了

D. Modelsim工程文件时mpf,打开工程的方法

以上几点是我收获比较大的地方,也是CB和一般书不一样的地方,他是真正把自己平常怎么做的告诉大家。为了更好的学习和体会到CB的风格,先试试Counter_Design这个设计。正好自己的新电脑装好了quartus II13.0和ISE14.6,modelsim10.1c,以及编译好了altera和xilinx的仿真库。开始!

工程仿真:modelsim半小时跟头,没仔细看CB书造成的。

1. 建立quartusII工程

A:关键养成之前的工程文件目录的习惯!这个接受起来不是很困难。

B:规范代码风格,这个一个很长远的话题,准备将CB打印出来,贴在电脑前,时刻提醒自己按照这个风格规范自己!

C:写完之后,先保存,在ctrl+k,不用全编译,因为我们需要做功能仿真,这样节省编译时间。PS:新电脑编译就是快。

2. 编写testbench

A:在notepad++中编写testbench文件,保存在sim中仿真的那个工程中。

B:规范代码风格,注意task 封装,task封装的好,移植性就强。

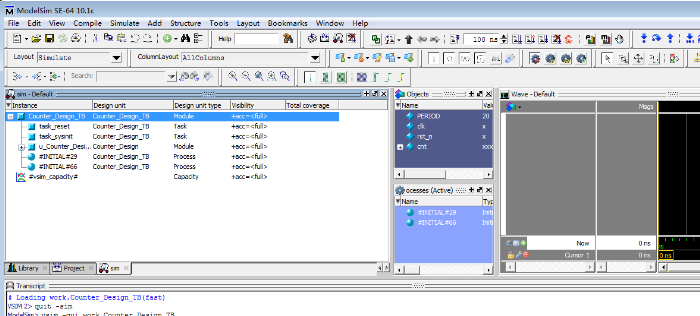

3. Modelsim仿真

A. 将需要测试的v文件也copy到sim目录下

B. 然后就是添加文件后进行仿真

4. 出现仿真问题

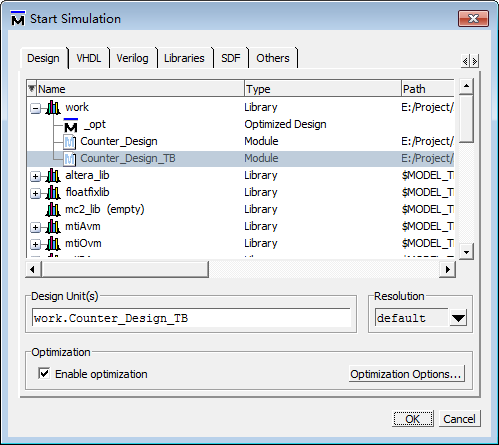

按照CB的步骤是没有什么问题的,但是就是在测试模块下面没有信号列表,仿真更别谈有波形了,无意中发现不应该勾选Enable Optimization

如果勾选的话,出现的是:

点击ok,你可以看到,没有信号。。。

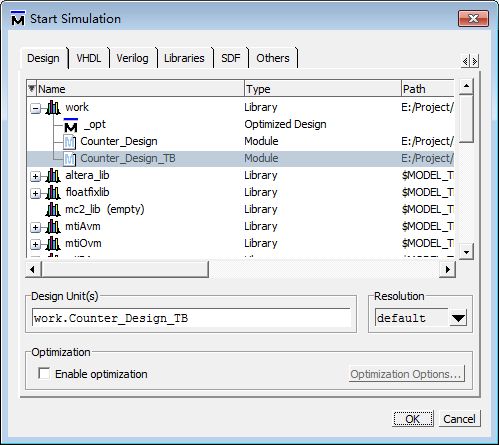

所以不要勾选:

然后去网上各种也是验证了这个东西,就是要去掉那个Enable Optimization

代码风格需要坚持下去

modelsim仿真要熟悉!