【基于Zedboard的图像采集教程】Zynq的图像采集及其显示

0赞Zynq是Xilinx大约3年前推出的最新可扩展处理平台,是一块可编程SoC芯片。不过也可以把它当成一块ARM芯片,FPGA用来完成ARM的外设功能。

因为本人是做图像方面工作的,所以本人从Zynq图像采集来了解该芯片的使用,以及在FPGA内的架构设计。也可能会说的不对,但尽量能给大家一些帮助。图1所示为鄙人用Zedboard做的MT9V022摄像头采集并显示的实例。

图1 用Zedboard做的MT9V022摄像头采集并显示

接下来开始基于Zynq的图像采集的第一部分,从宏观去分析该如何去做这个架构设计,第一篇主要以分析架构设计为主,而详细的实现过程将会在以后的文章中说明。让我们先来了解一下图像采集需要做的事情。

图像数据源可以来自图像传感器、VGA和HDMI等图像源。但都有基本上相同的特点,都可解码成垂直同步信号(VSYNC)、行同步信号(HSYNC)、图像数据(DATA)和数据有效信号(DE)。所以无论什么图像源,图像采集架构设计基本上是一样的。

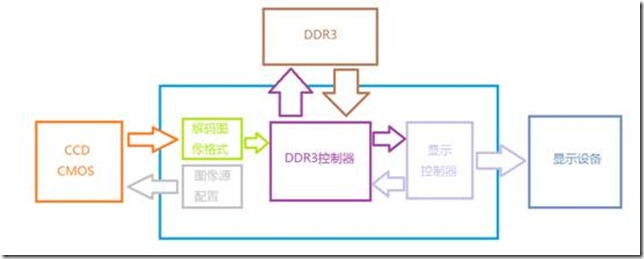

图像解码我们说完了,我们最终目的是想要显示图像,但显示设备的刷新率不同,时序不同,我们需要将图像数据放到内存中做帧缓存。接下来我们该明白要做什么了,要将图像放到内存中缓存。缓存后根据输出设备的时序从内存读出数据。此时我们就能在显示设备看到图像了,基本结构如图2所示。鄙人的语言表达水平很一般,具体的FPGA图像采集请看CrazyBingo的《从零开始走进OV7670世界》,看了一定会有很大的收获。

图2 图像采集和显示基本结构

图像采集的基本结构刚刚已经说完了,总结一下,图像采集几个重要的地方:(1)采集外部数据源解码;(2)数据放到DDR缓存;(3)从DDR读取数据显示。我们先记住这3个要点,接下来会用到。

现在我们回到Zynq这颗芯片,我们先简单地了解一下这颗芯片。因为对芯片如果都不了解,是根本无法发挥这颗芯片的优势的,或者说并不能掌控得了这颗芯片的使用。所以我们应该对这颗芯片要有了解, 这里说的有些啰嗦,但了解这个芯片的确非常重要,建议看了文章的初学者,一定要花些时间了解这颗芯片,这很重要,不要急于求成。鄙人也不希望随便把我自己做的Zynq的图像采集过程直接贴到网上,那样就没有意义的。伸手党是永远学不会的,所以我只在这里写教程。至于源码鄙人会找个合适的时间上传的。

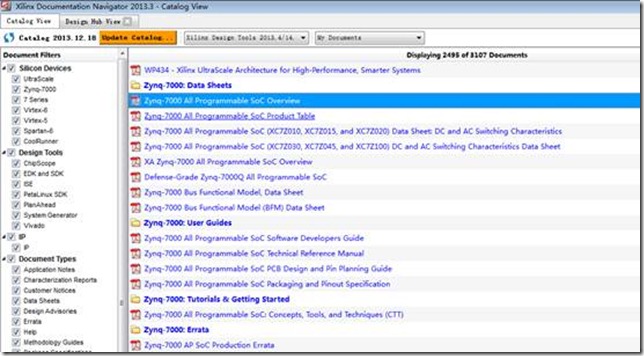

对于Zynq这颗芯片的介绍,官方的文档最权威,建议看Xilinx官方的文档,这里推荐下载一个Xilinx Documentation Navigator,是Xilinx的文档集成化工具,很方便,如图3所示。

图3 Xilinx Documentation Navigator

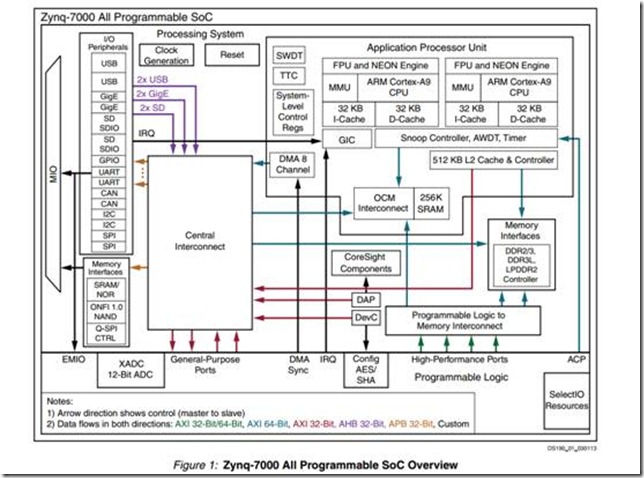

我们就来看《Zynq-7000 All Programmable SoC Overview》这篇文档的介绍来分析Zynq这颗芯片的基本架构,其实说了解架构有些复杂了,简单地说就是了解Zynq这颗芯片内部的ARM与FPGA之间是怎么交互的,这样才能让我们才可以很好地利用ARM与FPGA资源。

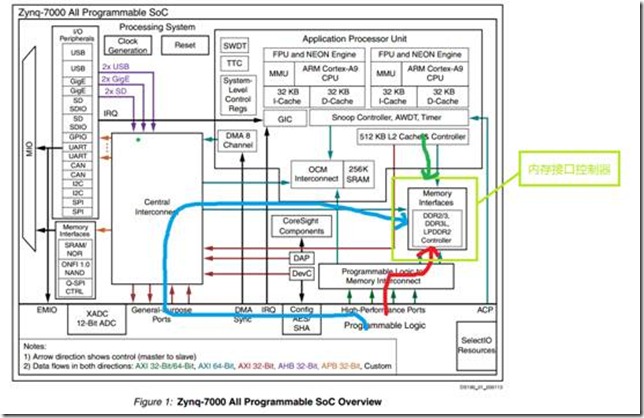

图4 Zynq的SoC整体架构图

图4是Zynq的SoC整体架构图,从图中我们能看到Zynq的资源还是很丰富的。先说(Processing System,PS)部分。两个ARM Cortex -A9;各自独立的32 KB缓存(I-Cache),以及两个个共享32 KB的缓存(D-Cache);片上ROM存储器;外部存储器接口(DDR、SRAM等均支持);8个通道DMA控制器;还有大量的外设和接口,例如以太网、USB2.0、CAN、I2C、SPI和UART等。可编程逻辑部分(Programmable Logic,PL),就是Xilinx 7系列的FPGA了。

这样来看,DDR3控制器是由PS控制的,当然也可以在PL部分挂一个DDR3,但这样ARM与FPGA就分开使用了,意义并非很大,但特殊应用除外。所以刚刚我们总结的图像采集三个重要的地方,第二点就是将图像放到内存中进行帧缓存。所以眼下要解决PL端的数据怎么能够进入到PS端控制的DDR3是很关键的。

我们依然看Zynq的整体结构图,内存接口控制器是个多端口访问,可以允许处理器与逻辑部分共享同一个内存。

原文是这样写的

连接到DDR3控制器有3种端口访问方式:

(1)一个端口是连接到ARM的二级缓存,经过64 bit的AXI总线接口连接到内存控制器。

(2)两个64 bit的AXI总线用于PL部分的访问。

(3)一个64 bit的AXI总线用于与连接被共享的AXI Master的访问。

原文是这样写的

图5 Zynq的SoC整体架构图说明

今天就写到这里,下一篇着重介绍PL部分如何访问内存的。

ChinaAET独家教程,未经许可,严禁转载