ZYNQ图像采集及其显示(二)

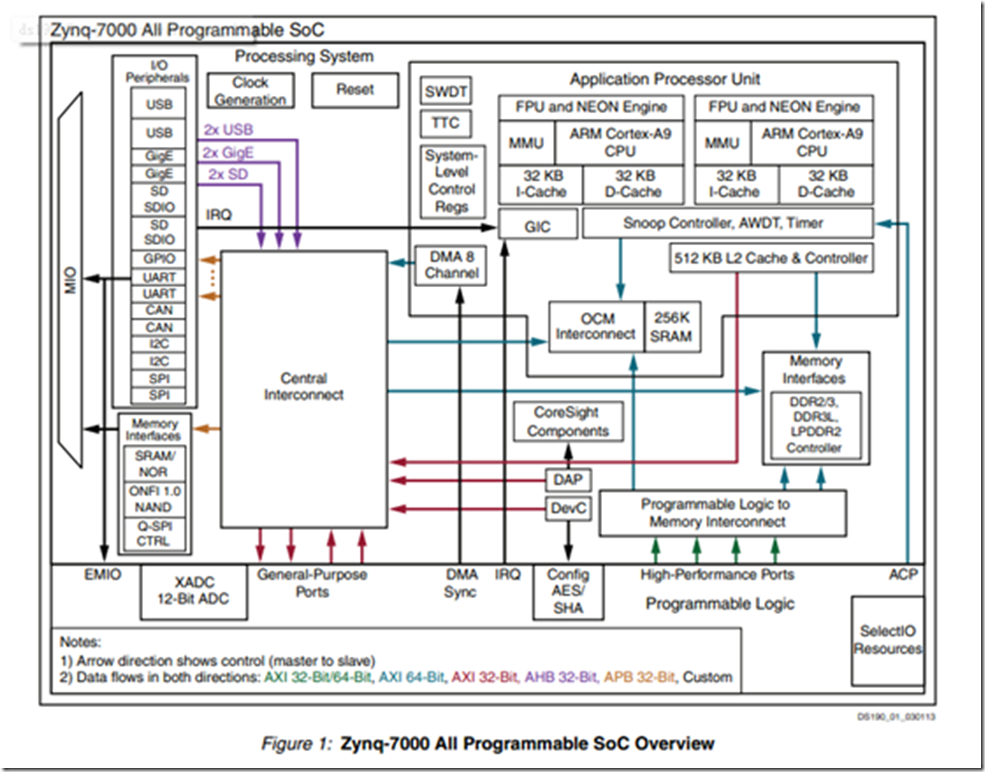

0赞上一章结尾写了ZYNQ访问内存三种方式,这里主要讲ZYNQ图像采集的,所以我们主要说一下其中一种方式,通过AXI High-Performance Ports总线(后面简称HP口)访问内存。下面我们来简单了解下,这里表示啰嗦几句,也照datasheet抄几句,毕竟对后来我们正式进入zynq图像采集有很大帮助。

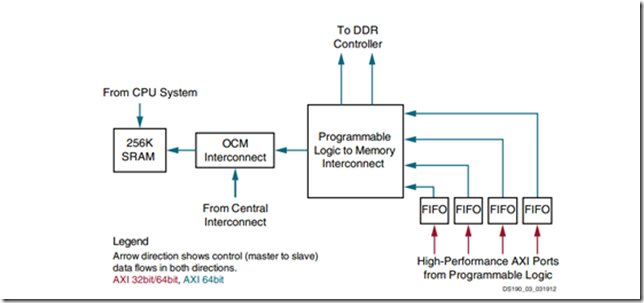

从图中看,PL可以通过HP口访问内存与OCM,下面上个图更直观些。从图中我们可以看到PL端通过FIFO连接到存储器互联接口上。

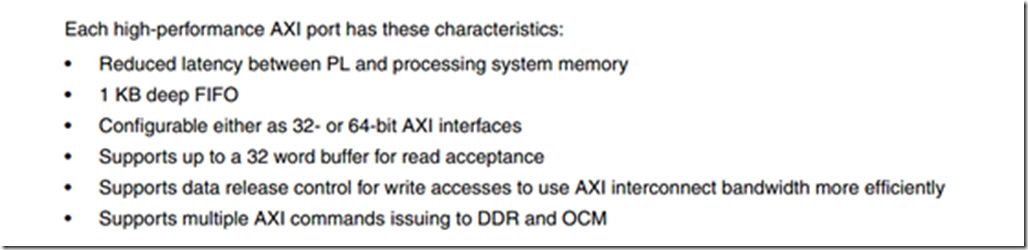

下面关于AXI HP接口的特性的官方原话:

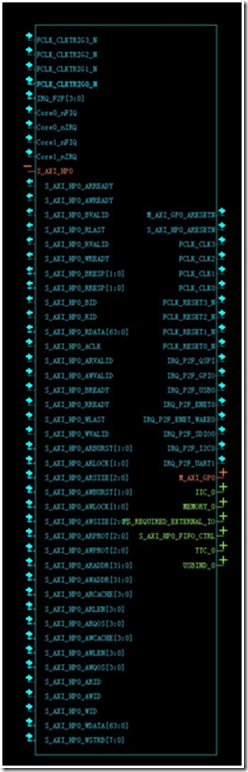

接口特性我们差不多看了,这块我们简单了解下就可以,因为PL的图像数据直接进入到HP口,这是件很麻烦的事情,我们可以看看他的接口。看下图,是不是有种不想用的冲动!!!

其实我们还有一种办法,连地址都不需要去管太多,但笔者还是建议大家以后直接操作HP口,因为后续的一种简单的方案虽说让问题变得简单化,但导致消耗将近4k逻辑,成本敏感的朋友,可能会很头疼,本来用7010的片子就可以完成设计,这下吃紧,仅仅能用7020的芯片。但不管怎么样,先能把基本的图像弄出来才是关键!!!

其实我们将PL数据放入内存中并非是直接将数据扔进去,然后不管了,我们还需要进行地址映射,事情越来越麻烦了。接下来我们看xilinx给我们提供的一个方案。

内存映射(memory map)其实已经做好了,xilinx为了方便内存管理,会把AXI接口的总线挂在AXI Interconnect IP上,AXI Interconnect IP可以进行统一的内存映射管理。这样我们解决了地址分配的问题,但仍然需要映射地址的方式将数据输入进来。

(注:AXI的总线这里就不介绍了,网上很多博文还有资料讲述这方面,我们这里仅仅看下AXI Stream接口。)

AXI有一种传输接口协议是AXI Stream接口方式,该接口对于用户来说,不需要关心地址。仅需要:帧开始(tuser),行结束(tlast),输出数据(tdata),输出有效(tvalid),输出准备好(tready)这五个信号。

时序图如下:

但是AXI Interconnect IP只能连接memory map传输,并不能直接连接AXI Stream接口数据,所以只能继续加一个AXI Stream转接到memory map的DMA,这就是官方的也有的Video DMA IP。

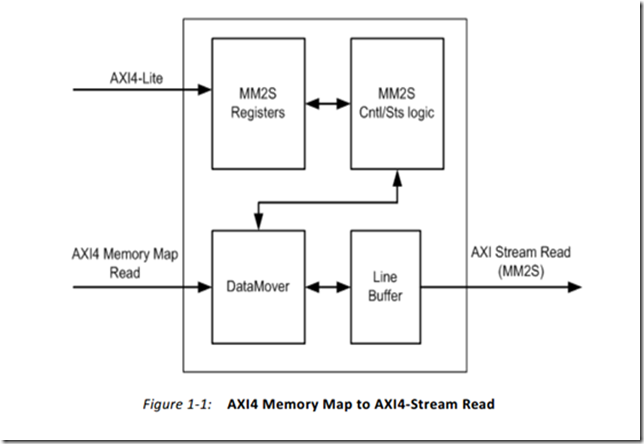

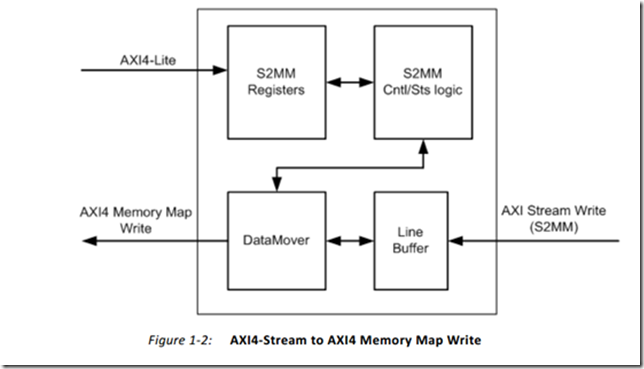

VDMA的结构如下图:

手册(PG020)上有这么个图,其实大概可以看出这么几个接口,AXI-lite,AXI Memory Map write,AXI Memory Map read,AXI Stream Write(S2MM),AXI Stream Read(MM2S)。

AXI-lite:作用是通过PS来配置VDMA ip。

AXI Memory Map write: 映射到存储器写

AXI Memory Map read:映射到存储器读

AXI Stream Write(S2MM):AXI Stream视频流写入图像

AXI Stream Read(MM2S):AXI Stream视频流读出图像

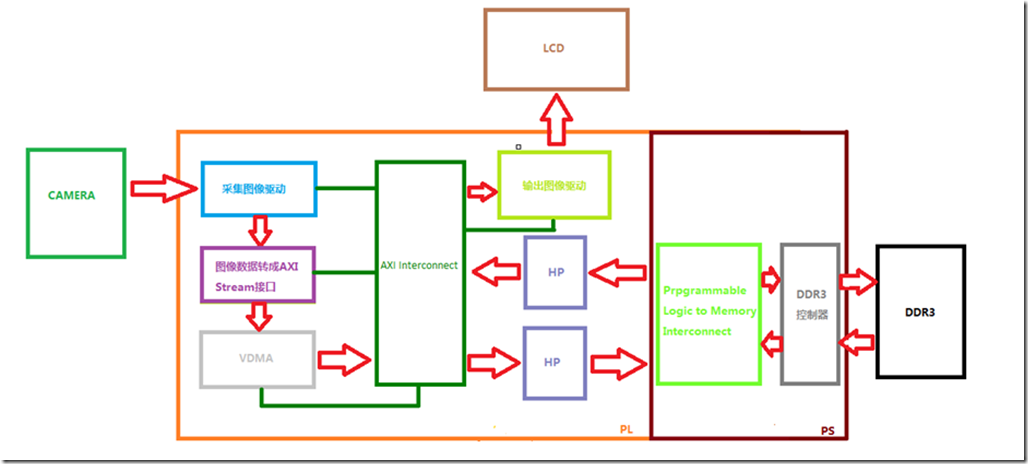

这样我们基本上大概知道视频流怎么进入到内存中了,先采集图像,然后图像数据转换成AXI Stream接口,然后通过VDMA转换成memory map,通过AXI Interconnect进入到HP口,通过HP口进入到Programmable Logic to Memory Interconnect,然后通过内存控制器进入到内存。如下图所示:

今天写到这里,下一篇开始搭建工程,正式进入ZYNQ图像采集之旅。