FPGA学习笔记一:实例详解FPGA开发流程

0赞Altera FPGA的开发流程大致包括以下,基本的主要包括以下十个方面的内容。本文将以一个简单的实际例子的设计来阐述这一开发流程,设计一个二选一数据选择器,来控制LED灯的亮灭。

*设计定义(明确设计的功能、目标和输入输出)

*设计输入(Quartus II、Notepad++)

*分析综合(Quartus II、Synopsys)

*功能仿真(Modelsim)

*布局布线(Quartus II)

*时序仿真(Modelsim)

*引脚分配(Quartus II、编写TCL脚本)

*烧写配置(Quartus II、USB Blaster)

*在线调试(SignalTap II等在线调试工具)

*板级验证(实物验证设计是否满足要求)

一、设计定义

设计定义二选一多路器,两个输入IO口,分别定义为a、b。可以是高电平,也可是低电平,当输入按键按下时,LED灯与a端口状态保持一致。输入按键释放时,LED灯与b端口状态保持一致。

二、设计输入

以Quartus II软件作为Verilog HDL语言的文本编辑平台,也可以根据自己的喜好选择Notepad++等第三方的代码编辑软件,只要支持Verilog HDL语言即可,一般来说还是Quartus II软件对Verilog HDL语言的支持最好。新建一个工程文件夹Lesson1如下图所示,包括Doc、IP、Prj、Sim、Src五个子文件夹,Doc主要用来存放与设计相关的参考文档等相关资料,IP主要存放与设计相关的IP核,Prj主要用来存放Quartus II工程文件,Sim主要用来存放testbench的仿真脚本,Src主要用来存放Verilog HDL源码,如下

二选一数据选择器Verilog HDL代码如下

1 module led_test(a,b,key_in,led_out);

2

3 input a; //输入端口

4 input b; //输入端口

5 input key_in; //按键输入,选择通道

6 output led_out; //led输出控制

7

8 assign led_out = (key_in == 0)?a:b ;

9

10 endmodule

三、分析综合

Quartus II的分析综合功能主要是供用户检查代码是否有语法错误以及关键字等的拼写错误。在做功能仿真之前要先对代码进行分析与综合。

四、功能仿真

功能仿真也叫布线前仿真,即仅仅为了验证代码的逻辑功能是否正确而做的仿真,他不考虑逻辑电路在实际中的延时特性。下面是为了测试所设计的二选一数据选择器而编写的测试代码,测试代码主要包括以下几个方面:a.延时单位与仿真精度、b.激励信号端口的定义、c.待测信号端口的定义、d.待测试模块的例化、e.产生激励信号。

1 `timescale 1ns/1ps //延时单位与仿真精度

2

3 module led_test_tb;

4 //激励信号的定义,对应待测试模块的输入端口

5 reg a;

6 reg b;

7 reg key_in;

8

9 //待测信号定义,对应待测试模块的输出端口

10 wire led_out;

11

12 //例化待测试模块

13 led_test u0(

14 .a(a),

15 .b(b),

16 .key_in(key_in),

17 .led_out(led_out)

18 );

19 //产生激励信号

20 initial

21 begin

22 a = 0; b = 0; key_in = 0;

23 #100;

24 a = 0; b = 0; key_in = 1;

25 #100;

26 a = 0; b = 1; key_in = 0;

27 #100;

28 a = 0; b = 1; key_in = 1;

29 #100;

30 a = 1; b = 0; key_in = 0;

31 #100;

32 a = 1; b = 0; key_in = 1;

33 #100;

34 a = 1; b = 1; key_in = 0;

35 #100;

36 a = 1; b = 1; key_in = 1;

37 #200;

38 $stop;

39 end

40 endmodule

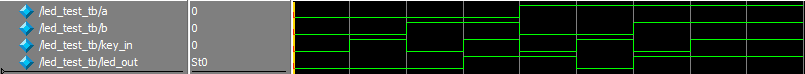

下面是运行Modelsim软件得出的仿真波形。

Key_in为低电平时,即按键被按下时,led_out与a端口电平一致,按键弹起时,led_out与b端口电平一致。可见逻辑设计是正确的。

五、布局布线

布局布线主要是有Quartus II软件自动完成,通过运行全编译,Quartus II会自动完成分析综合、布局布线等一系列操作。

六、时序仿真

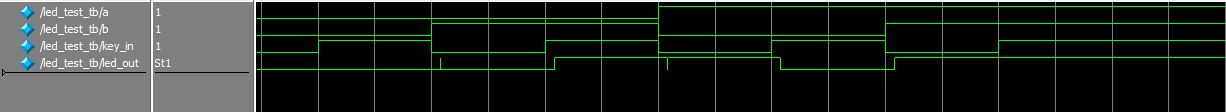

在布局布线完成后,我们运行 Gate Level Simulation,即可得到门级仿真(也即是时序仿真)波形,如下图所示

可以看到,门级仿真存在毛刺和延时,可见,在布局布线以后更能反映电路运行的实际情况。

接下来,放大波形测量毛刺宽度,如下图

可以发现,毛刺的宽度为0.461ns。

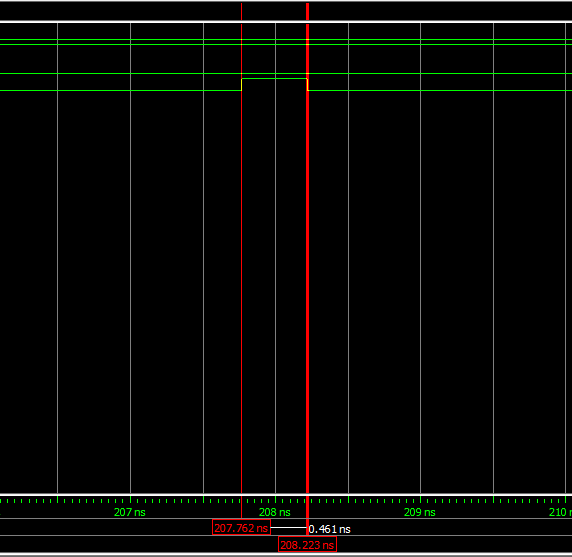

下面来测试一下输入和输出之间的延迟时间,如下图

延迟8.045ns,主要是由于布局布线后门电路的延迟所造成的。

七、引脚分配

引脚配置的方式有很多,可以通过TCL脚本进行配置,也可以直接在Quartus II软件的Pin Planer界面下进行引脚分配。

八、烧写配置

代码的烧写配置在Quartus II软件下借助于USB Blaster进行烧写,可以固化到Flash中,也可直接烧写到FPGA中,前者掉电后数据不丢失,后者掉电后数据丢失需要重新配置。

九、在线调试

主要是借助Quartus II软件所提供的嵌入式在线分析工具进行在线调试。比如SignaTap II等。

十、板级验证