FPGA学习笔记三:时序逻辑电路的设计与仿真验证

0赞一、以Quartus II软件和Modelsim软件作为代码设计与波形仿真平台,对一个简单的时序逻辑电路进行设计与验证。下面是该电路实现的HDL代码,完成一个LED灯秒闪。

module counter(clk,rst_n,led_out);

input clk;

input rst_n;

output reg led_out;

reg [24:0]cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 25'd0;

else if(cnt == 25'd24_999_999)

cnt <= 25'd0;

else

cnt <= cnt + 1'b1;

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

led_out <= 1'b0;

else if(cnt == 25'd24_999_999)

led_out <= ~led_out;

else

led_out <= led_out;

end

endmodule

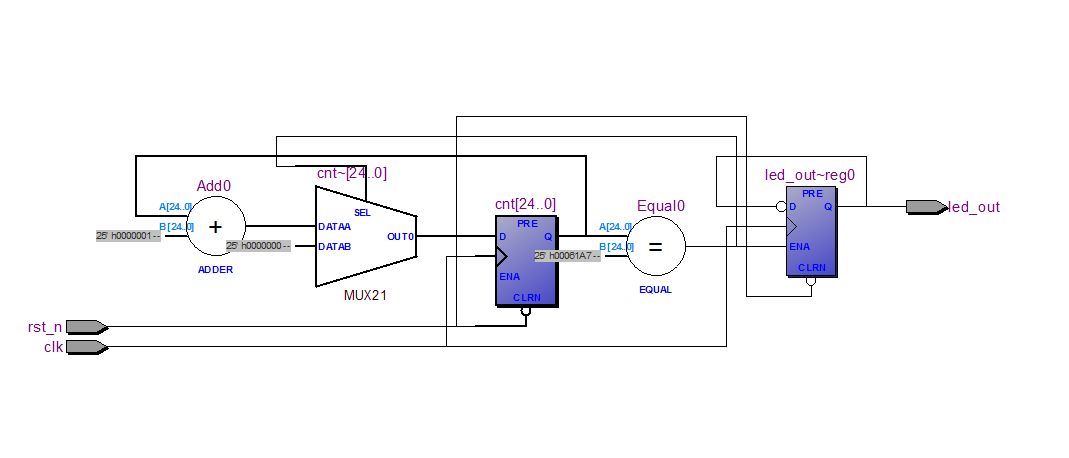

二、 译码器的RTL结构视图

三、计数器的Testbench

`timescale 1ns/1ns

`define clk_period 20

module counter_tb;

//定义激励信号端口

reg clk;

reg rst_n;

//定义待测试信号端口

wire led_out;

//例化待测试模块

counter u0(

.clk(clk),

.rst_n(rst_n),

.led_out(led_out)

);

//产生激励信号

initial clk = 1;

always #(`clk_period/2) clk = ~clk;

initial

begin

rst_n = 1'b0;

#(`clk_period*200);

rst_n = 1'b1;

#20000000;

$stop;

end

endmodule

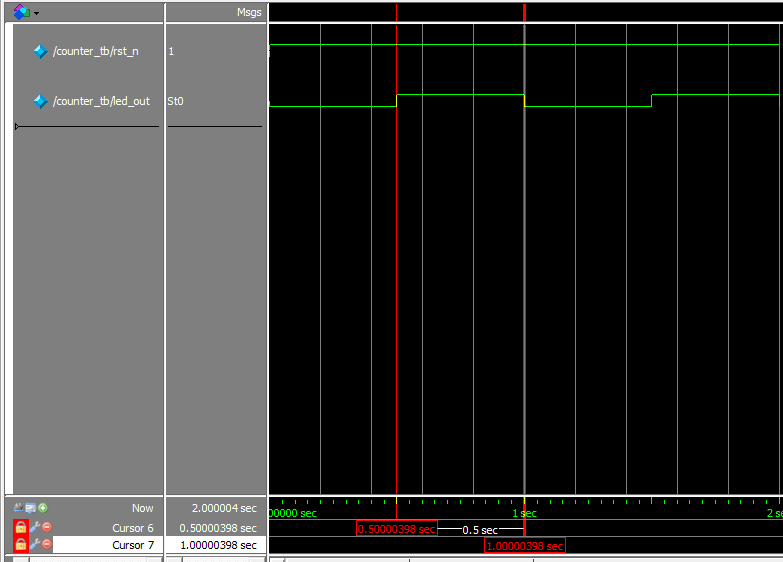

四、 仿真验证

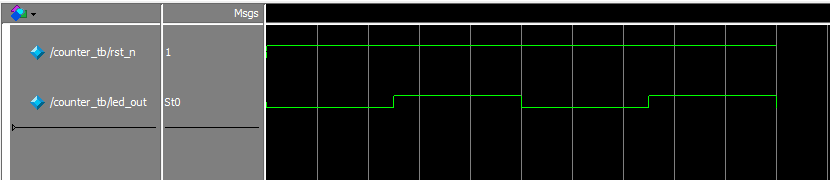

功能仿真(布线前仿真)波形如下

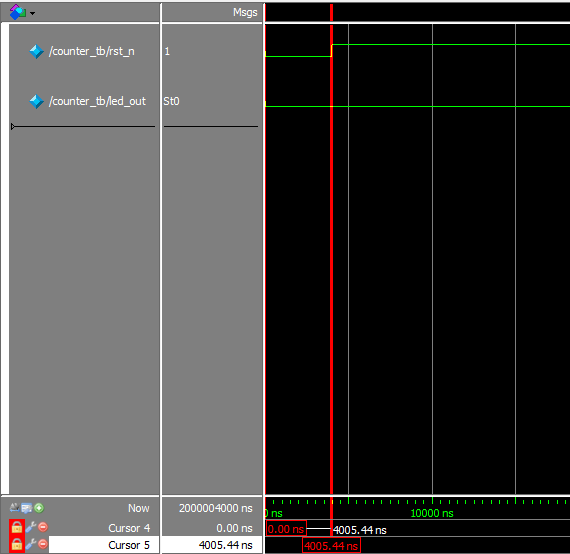

功能仿真起始时间处复位信号的延时释放,延时了4000ns,如下

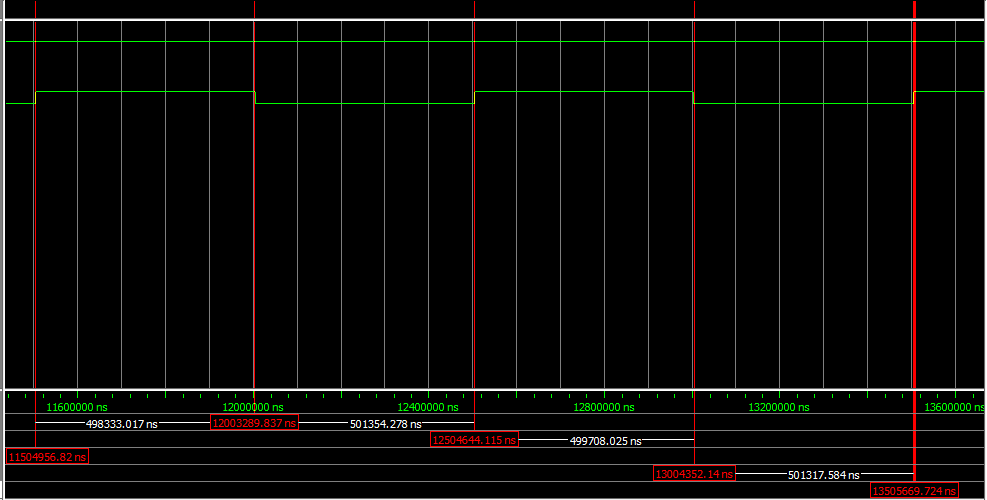

功能仿真时间测量,每500ms(0.5s) led_out输出翻转一次,如下

时序仿真(门级仿真)波形个如下,从图中可以看出,经过布局布线以后,信号发生了延迟,不再是准确的每500ms led_out输出翻转一次了。