FPGA学习笔记二:组合逻辑电路的设计与仿真验证

0赞一、以Quartus II软件和Modelsim软件作为代码设计与波形仿真平台,对译码器

进行设计与验证。下面是译码器实现的HDL代码

module decoder(x,y,z,out);

//输入端口的定义

input x;

input y;

input z;

//输出端口的定义

output reg [7:0]out;

always@(x,y,z)

begin

case({x,y,z})

3'b000: out = 8'b00000001;

3'b001: out = 8'b00000010;

3'b010: out = 8'b00000100;

3'b011: out = 8'b00001000;

3'b100: out = 8'b00010000;

3'b101: out = 8'b00100000;

3'b110: out = 8'b01000000;

3'b111: out = 8'b10000000;

endcase

end

endmodule

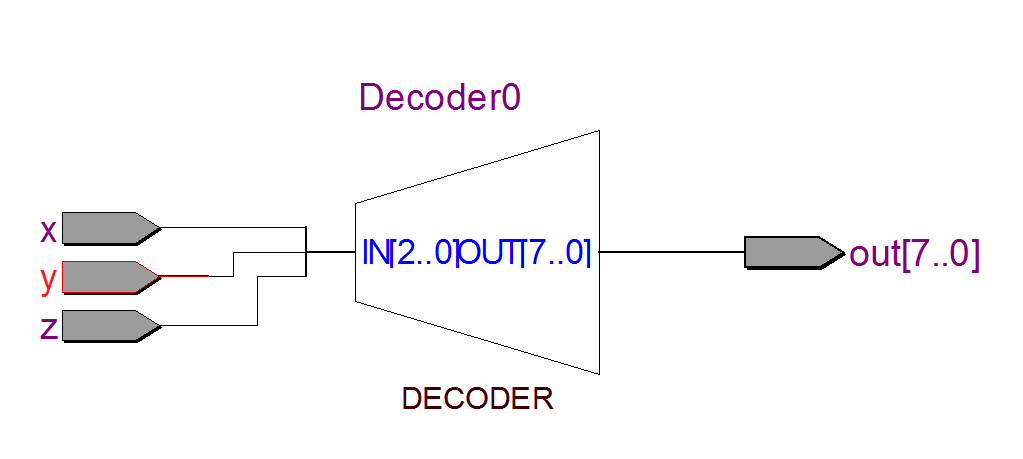

二、译码器的RTL结构视图

三、译码器的Testbench

`timescale 1ns/1ns //定义仿真时间单位和精度

module decoder_tb;

//激励信号端口定义

reg x;

reg y;

reg z;

//待测信号端口定义

wire [7:0] out;

//待测模块例化

decoder u0(

.x(x),

.y(y),

.z(z),

.out(out)

);

//激励信号的产生

initial

begin

x = 0;y = 0;z = 0;

#100;

x = 0;y = 0;z = 1;

#100;

x = 0;y = 1;z = 0;

#100;

x = 0;y = 1;z = 1;

#100;

x = 1;y = 0;z = 0;

#100;

x = 1;y = 0;z = 1;

#100;

x = 1;y = 1;z = 0;

#100;

x = 1;y = 1;z = 1;

#100;

$stop;

end

endmodule

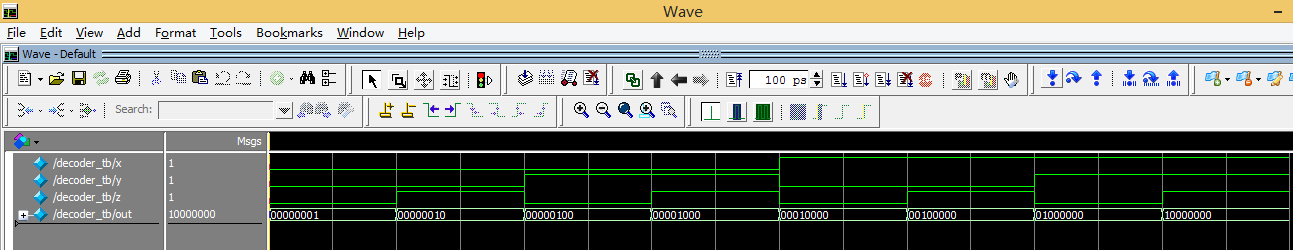

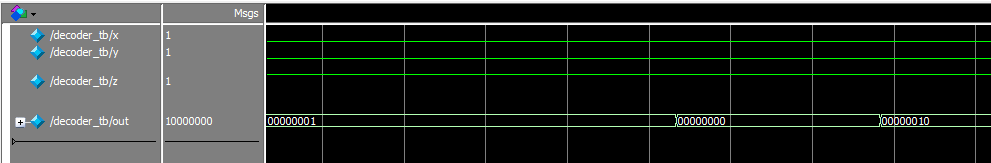

四、仿真验证

功能仿真(布线前仿真)波形如下

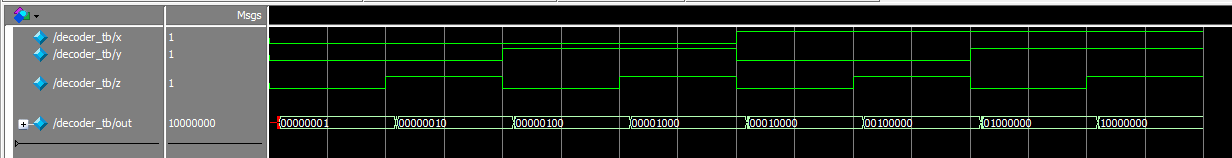

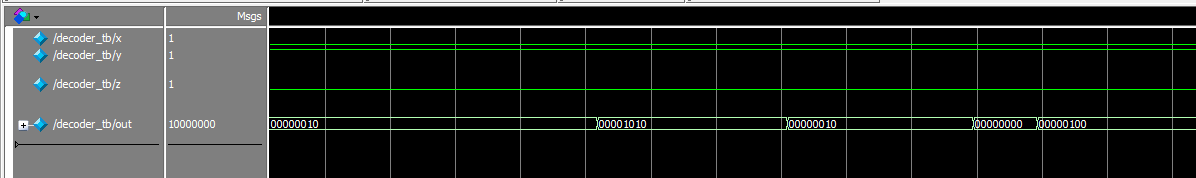

时序仿真(门级仿真)波形个如下

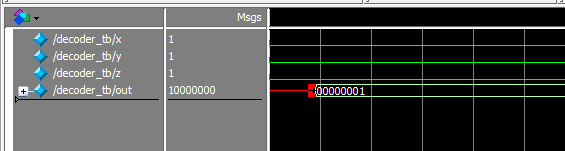

发现在每次输出发生变化前都出现了几个暂态,且在开始变化时有一段不确定状态,如下图

从上图中可以看出起始部分出现了不确定状态。

由0000 0001变化到0000 0010的过程中出现一个暂态0000 0000之后才变成了0000 0010,这是由电路内部的结构决定的,说明在这个电路中第0位数据由1->0变化的时间比第1位数据由0->1变化得快,所以出现了0000 0001->0000 0000->0000 0010这样一个变化过程,再来看由0000 0010变化到0000 0100过程中出现的暂态,如下图

上图中出现了0000 0010->0000 1010->0000 0010->0000 0000->0000 0100的变化过程,出现了三个暂态。