In-System Sources and Probes Editor

0赞

本文来自SF-CY3 FPGA套件开发指南Ver7.20 (by特权同学).pdf

In-System Sources and Probes Editor,这种方式是通过例化一个定制的寄存器链到 FPGA 器件内部。这些寄存器链通过 JTAG 接口与 Quartus II 通信,它又能够驱动 FPGA 器件内部的某些输入节点信号,采样某些输出节点信号。这就使得调试者不用借助外部设备就能够给 FPGA 添加激励并观察响应。

In-System Sources and Probes Editor 例化

In-System Sources and Probes Editor 可以简单的将 FPGA 内部的某些输入或输出信

号接口引出,在 Quartus II 中便可对其进行在线的读写操作。它给系统调试带来的便利可

见一斑。通常,我们可以通过 In-System Sources and Probes Editor 实现以下的一些在线

验证和测试功能。

● 创建虚拟开关功能,便于控制 FPGA 内部逻辑功能的运行情况

● 创建虚拟面板指示功能,便于观察 FPGA 内部逻辑功能的一些简单状态指示

● 便于直接引出某些状态量进行观察

● 随时更改内部功能逻辑的状态

因为 In-System Sources and Probes Editor 是 Quartus II 中的一个 IP 核,所以我们需要先对其进行设置添加,然后例化到我们的代码中。

1、点击菜单栏 ToolsMegaWizard Plug-In Manager。

2、选择 Create a new custom megafunction variation。

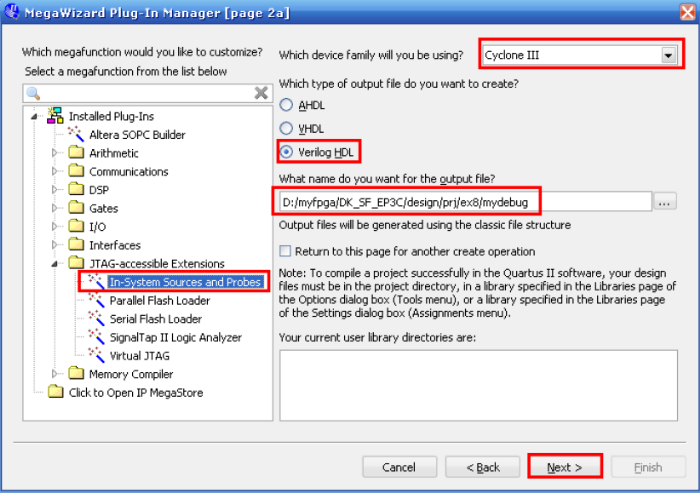

3、在 MegaWizard Plug-In Manager 中,做如图所示的设置,注意在 What name do you want

for the output file 中,需要输入一个该代码的文件名,如这里在工程目录 ex8 后面命名

mydebug。最后点击 Next 进入下一步。

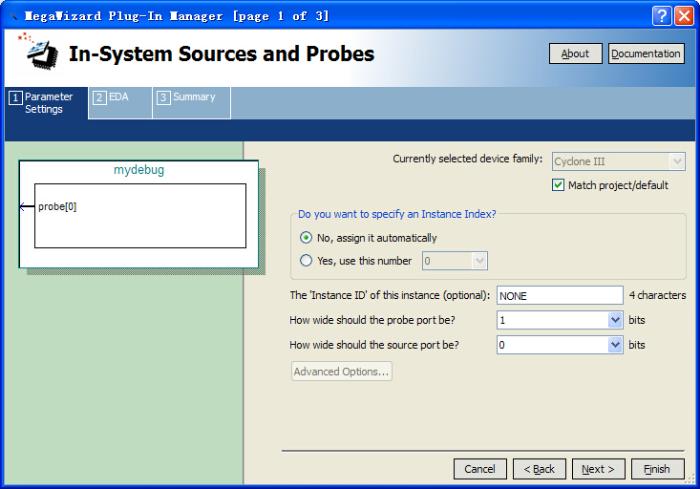

4、如图所示,我们需要在 In-System Sources and Probes Editor 配置页面中,设置 probe port为 1bits,source port 为 0bits。Probe 的功能是读出(对于工程设计为输出)我们的 FPGA 设计中的某些寄存器,而 source 则是写数据(对于工程设计为输入)到 FPGA 设计中。本实例是要实时监控查看输出的 LED灯闪烁的状态,所以选择 probe。完成设置选择 Next。

5、第二步 EDA 不需要做设置,我们来到 Summary 配置页面,注意要勾选 mydebug_inst.v

文件,这个文件里面有 In-System Sources and Probes Editor 的例化模板。完成这些设置后,

点击 Finish 完成所有配置。

LED灯 Verilog 参考代码

module led

(

input clk,

input rst_n,

output led_out

);

reg [23:0]cnt = 24'd0;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 24'd0;

else

cnt <= cnt + 1'b1;

end

reg led_flag = 1'b0;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

led_flag <= 1'b0;

else if(cnt[23] == 1'b1)

led_flag <= ~led_flag;

end

mydebug mydebug_inst (

.probe ( led_flag ),

.source ( )

);

assign led_out = led_flag;

endmodule

6、仿真验证(simulation不罗嗦)

7、引脚分配全编译

8、时序约束

(1)点击TimeQuest Timing Analyzer

(2)点击菜单栏 NetlistCreate Timing Netlisk,弹出的菜单中使用默认设置,点击 OK 便可。

(3)接着进行时钟约束,点击菜单栏 ConstraintsCreate Clock。Clock name 是我们随便给约束的信号起的名字,没有特别限制;Period 为时钟周期,我们的时钟晶振是 50MHz 的,即 20ns;Targets 选择实际被约束的时钟引脚,点击改行最后面的按钮可以选择相应的引脚信号;SDC command 无须设置,自动根据前面的设置生成,Waveform edges 也无须设置,我们采用默认设置,即 0ns 时钟上升,20ns 下降。点击 Run 完成约束设置。

(4) 接下来,我们要依次点击主界面右下方 task 栏里的 Update Timing Netlist 和 Write SDC File选项,弹出的 Write SDC File ,我们更改 SDC file name 为 led.sdc,接着点击 OK。

(5)此时,我们可以在工程目录下找到一个 ex0.sdc 的文件,并且这个文件里面有一条这样的时钟约束语句:create_clock -name {SYS_CLK} -period 20.000 -waveform { 0.000 10.000 } [get_ports {clk}]。这便是我们前面所添加的约束。

(6)接着回到 Quartus II,重新对工程进行编译。接着再进入 TimeQuest,点击 Report 下的Report All Core Timings。

9、下载配置文件

10、 接下来使用 In-System Sources and Probes Editor 进行调试,点击菜单栏的ToolsIn-System Sources and Probes Editor。

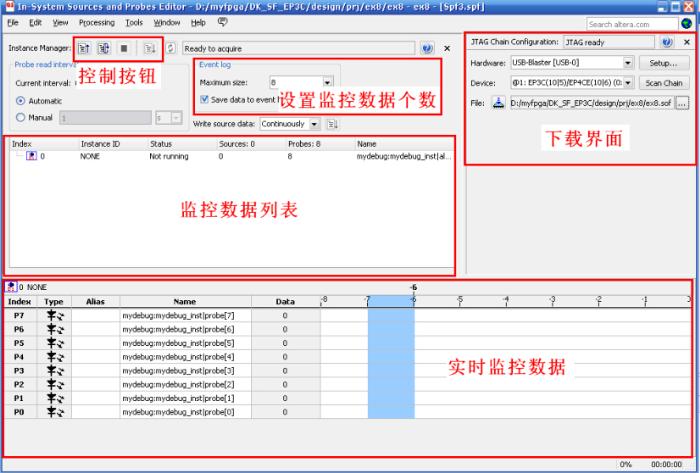

In-System Sources and Probes Editor 的主界面如图所示。

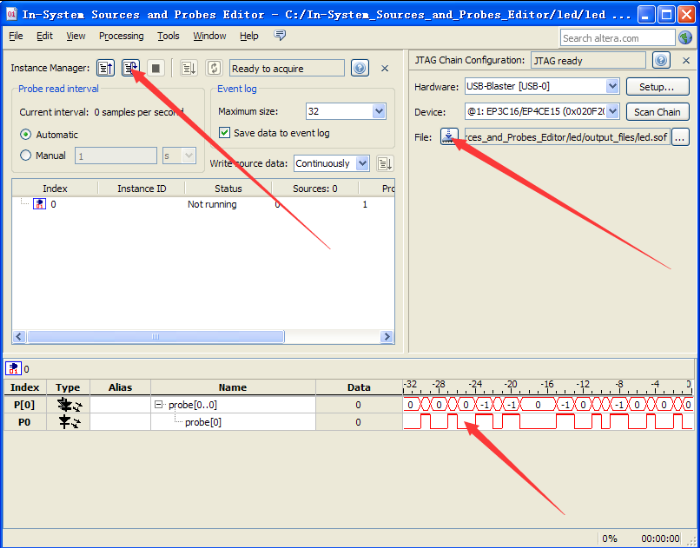

11、如果还未使用 Programmer 执行过下载操作,可以如图所示在 In-System Sources and Probes Editor 界面中执行。

最后,我们设置监控数组为 32(当然也可以更大,这个设置就是监控窗口中显示出来的数据个数),点击持续监控的按钮,开始数据捕获。如图所示,对应的 led 电平值也持续的变化了。