基于FPGA的原理图PCB设计【连载2】——原理图设计

0赞我的开发工具:Cadence 16.6,所用 FPGA为Altera家的。

画FPGA原理图需准备以下资料:

(1) 原理图库文件

(2) 芯片手册

(3) Pin out file

原理图库文件可以从官网上下载,比如我用cadence画Altera家EP4CE115F29I7N原理图,就直接下载EP4CE115.OLB文件。

https://www.altera.com/support/support-resources/download/board-layout-test/pcb/pcb-cadence.html

原理图中,这种大量管脚的芯片一般分为多个part,包括电源、地、各个bank、配置等。

芯片手册几乎给出了关于这个芯片设计(Cyclone IV Device Handbook)的所有需注意的问题,包括配置方式、全局时钟网络、专用时钟接口、lvds接口等。

pin out file中有每个管脚的详细说明。

(1)芯片配置

配置方式主要有JTAG或AS模式我只预留JTAG接口,有些板子上预留了两个下载接口,一个JTAG,用于下载程序,一个AS,用于固化程序,感觉这样很麻烦,我在固化时选择JIC(JTAG Indirect Configuration File)文件,尽管相对于AS模式会固化程序会慢一点,但毕业还是JTAG方式,这样就省去了烦琐的AS模式。

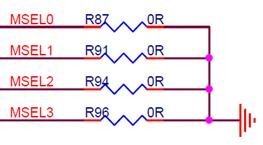

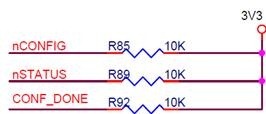

JTAG方式有用的信号其实就4个:TCK(测试时钟)、TDO(测试数据输出)、TMS(测试模式选择)、TDI(测试数据输入),再加上VCC和GND,共6根线,所以其实可以把标准10pin下载口简化为6pin,标准10pin下载口体积大,而6pin连接器可以自己选择,这样更方便。nConfig、nStatus、CONF_DONE、TMS、TDI需要上拉,TCK需要下拉。

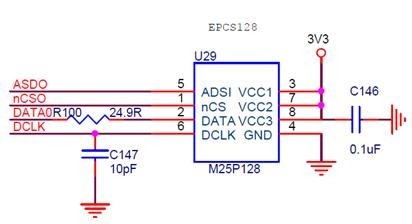

配置芯片一般为EPCS系列,如EPCS64,EPCS128,相应地,可以用ST公司的M25P64和M25P128代替,连接方式如下图所示。

画完原理图,一定要检查下面16个管脚,连接是否正确,否则,板子很可能不工作

(2)专用时钟

专用时钟输入与输出的选择仍然需要参考,首先,专用时钟输入管脚都是可以驱动内部PLL的,可以配置为普通IO输入,但不能配置为输出管脚,之前有一次就因为没太注意,把这个管脚用作了输出,结果板子出了问题。而专用时钟输出管脚,可以用于普通IO输出,也可以用于时钟输出。设计时,最好是把专用时钟输入管脚全部用作时钟输入,把专用时钟输出管脚全部胜任专用时钟输出,毕竟,IO资源一般不会这么紧张。

(3)lvds设计

关于lvds设计,需要仔细看技术手册和Pin-Out Files for Altera Devices,下载地址:

https://www.altera.com/support/literature/lit-dp.html#Cyclone-IV

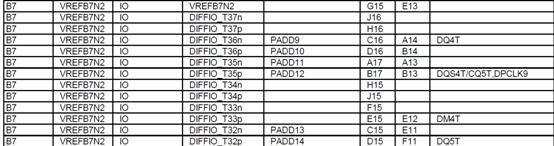

对于c4,rx和tx复用,见Cyclone IV Device Handbook第133页,从pin out file里也可以看出,P和N都是确定好了的,如DIFFIO_T35P和DIFFIO_T35N。

而对于c5器件,存在专用lvds通道,rx和tx是分开的,例如DIFFIO_RX_B1P和DIFFIO_RX_B1N为一对。

关于lvds部分的具体设计,在另一个专题lvds技术连载中会涉及到。

到这里,关于FPGA设计原理图部分基本上是说完了。