串口线制作兼max3223使用

0赞串口通信使用起来非常方便,在主机与FPGA的通信上用的非常广泛,但普通DB-9接口尺寸太大,占用电路板很大面积,而使用自定义接口,将会大大减小占用面积,并且使用起来也很方便。

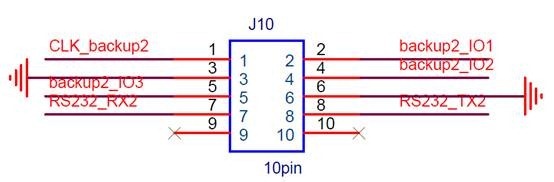

在设计中,我定义了一个8pin的接口,使用JST连接器,预留有专用时钟输出,通用IO口,另外,还有一组RS-232串口。

我需要从8根线中接出3根用作串口,那么串口线应该怎么做呢?

先来点基础知识,我用的串口转USB线如下图所示,DB9M(公头)接口,当然,也有USB转DB9F(母头)接口,下面针对USB—DB9M串口线来说。

上张管脚顺序图

DB9串口连接器管脚定义如下

针脚 | 定义 | 符号 |

1 | 载波检测 | DCD |

2 | 接收数据 | RXD |

3 | 发送数据 | TXD |

4 | 数据终端准备好 | DTR |

5 | 信号地 | SG |

6 | 数据准备好 | DSR |

7 | 请求发送 | RTS |

8 | 清除发送 | CTS |

9 | 振铃提示 | RI |

接下来说说max3223串口通信芯片,这个芯片是一个2通道串口通信芯片,可实现TTL和RS-232电平的转换,下面这张图很清楚地说明了该芯片的使用方法,我就不多哆嗦了。

对于RS-232通信,做串口线时只需连3根线即可。

pin2 RXD 对应电脑数据接收端,连到max3223的232输出T1OUT或者T2OUT

pin3 TXD 对应电脑数据发送端,连到max3223的232输入R1IN或者R2IN

pin5 SG 对应信号地

做了一根串口通信线,一端为DB9F接口,另一端连到自己定义的8pin JST连接器上。

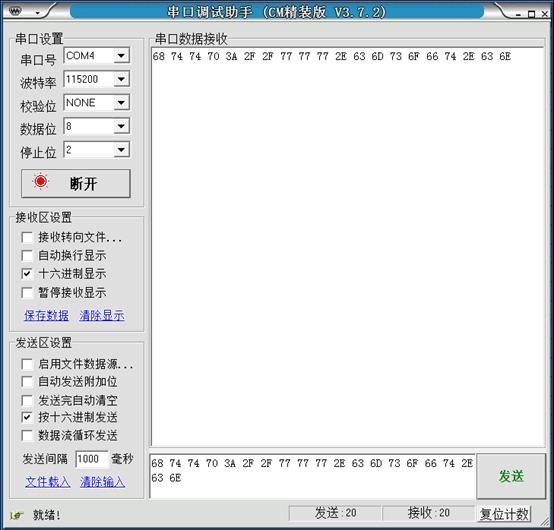

最后就是实验测试了,115200 baud,COM4,2位停止位。发送20个字节,接收20个字节,ok,调试完成!!

FPGA部分的代码前面博文中有过说明,可在逻辑中编写verilog来实现,也可以在nios中使用uart核来做。