Diamond中的IPexpress入门教程

0赞

发表于 7/4/2017 9:22:13 PM

阅读(12352)

IPexpress是Lattice官方提供,集成与Diamond中的一些IP核,可以通过简单的配置以生成VerilogHDL或者VHDL的代码,以供用户实例化(调用)。一些芯片中的功能推荐使用(甚至只能使用)IPexpress来生成代码,比如RAM、FIFO、SERDES、PLL等。该功能类似于Altera的LPM、Xilinx的CoreGenerator。

下面以MachXO3器件为例,讲解一下如何通过IPexpress功能来调用PLL进行倍频。MachXO3的官方Demo板上的晶振为12Mhz,我们将通过程序实现5倍频,得到60Mhz的信号。本篇博文只讲解IPexpress部分内容,程序综合过后的仿真结果将在接下来介绍ActiveHDL仿真的时候讲解!

下面是详细步骤:

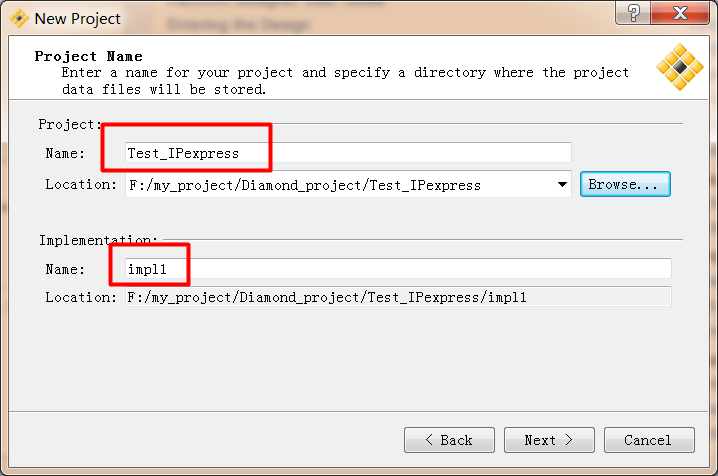

1、首先新建工程Test_IPexpress;

2、选择MachXO3,并选择LSE为综合工具(第三方综合工具的使用方法,将在后续的博文中介绍);

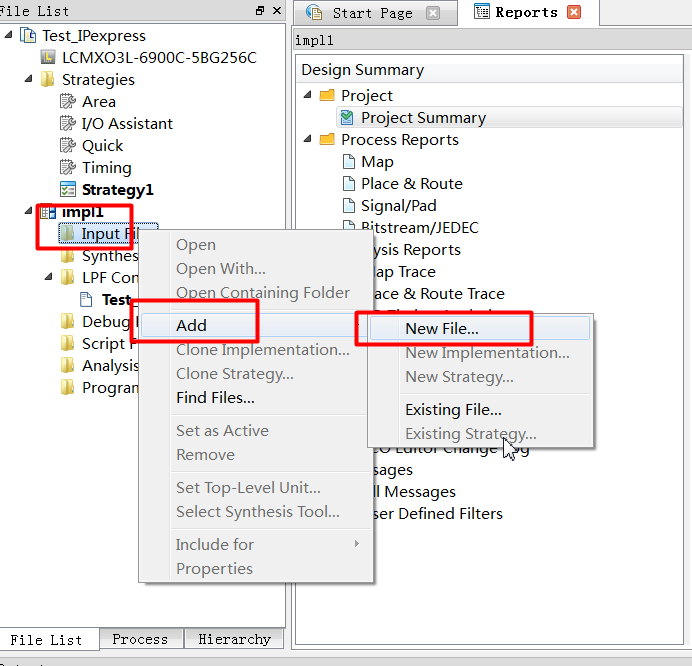

3、右击Input文件夹,Add->newFile;

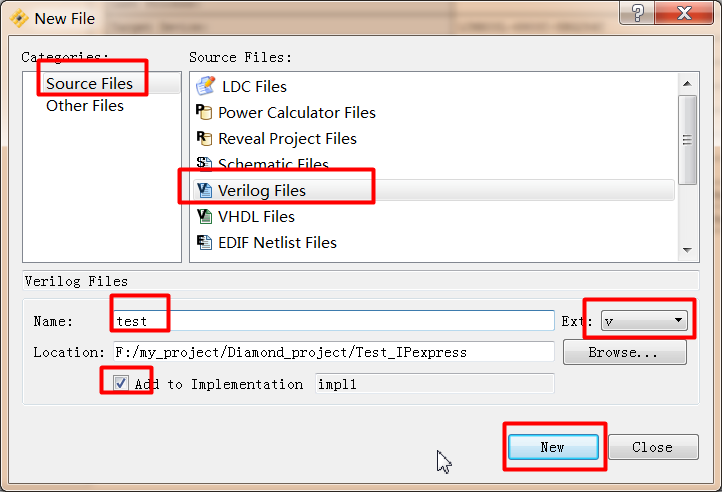

4、创建test.v,作为顶层文件;

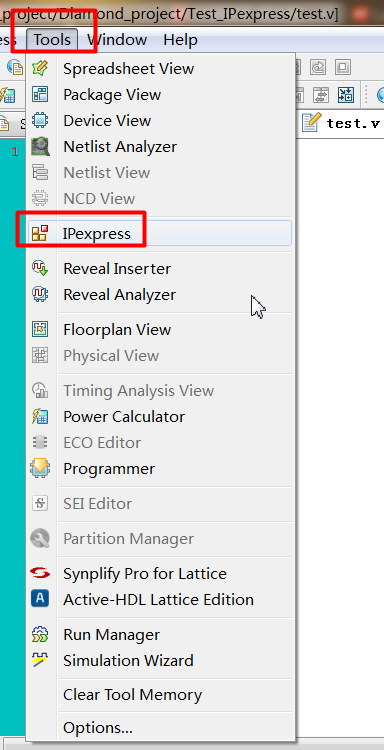

5、点击Tools->IPexpress,或者直接单机工具栏图标;

6、点击PLL,然后在右侧输入my_pll,并选择Verilog;

7、在左侧输入实际输入频率:12M,右侧输入期望频率60M,并点击计算,随后点击生成;

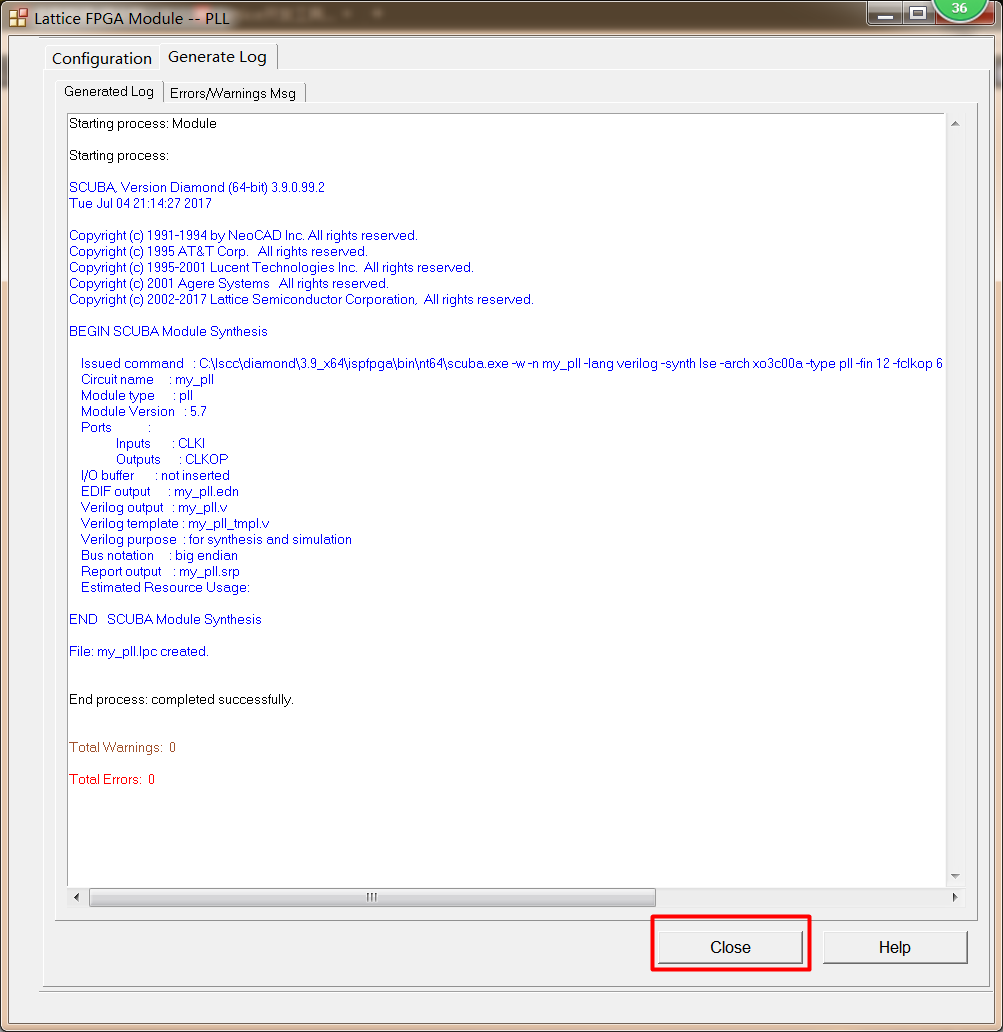

8、之后会出现该界面,直接关闭即可;

9、添加已存在文件;

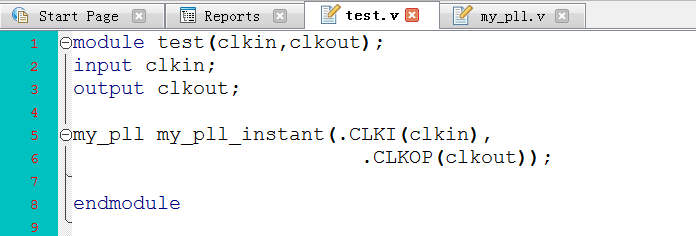

10.选择刚才生成的my_pll.v,并在test.v中输入如下代码;

11、然后进行综合;

说明:本程序的仿真部分将在后续博文中展示。