一种Low Latency的整数除法器设计

2赞

发表于 1/4/2018 5:06:32 PM

阅读(3298)

之前写过两篇关于除法器的文章了(http://blog.chinaaet.com/justlxy/p/5100052322和http://blog.chinaaet.com/justlxy/p/5100052068),今天来介绍一种全新的设计思想,这种设计的优势是可以用较少的资源同时实现高速度、低Latency的要求。与此同时,其缺点也很明显,只适用于除数位宽比较低的情况(比如1~8bits)。

传统的除法器基本上都是采用移位加减的方式来实现除法运算的,这种设计也可以实现很高的运算速度,但是需要很多个Latency。如果需要降低Latency的话,可以把部分移位的操作进行迭代,代价是运算速度会显著降低。

今天来介绍的这种设计思想其实很简单,举个例子来说,我们想计算y = k / x,实际上可以等价于y = k * (1/x)。当除数(也就是x)的位宽比较低的时候,我们可以预先计算好每一个1/x的值,并把其放入ROM中,作为查找表使用。

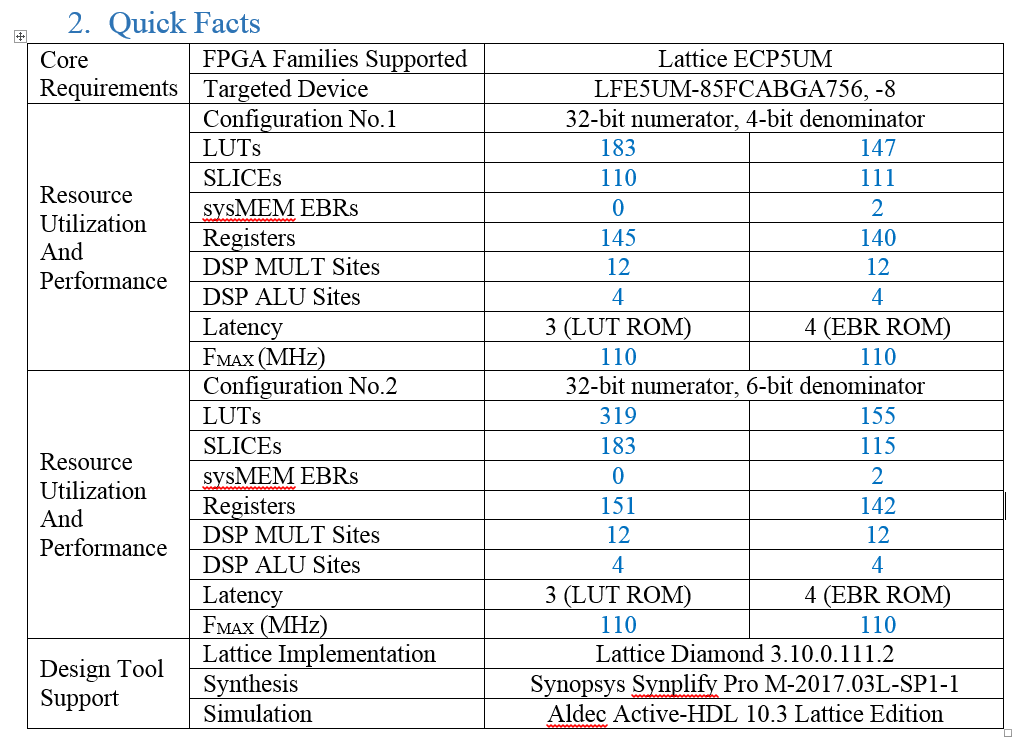

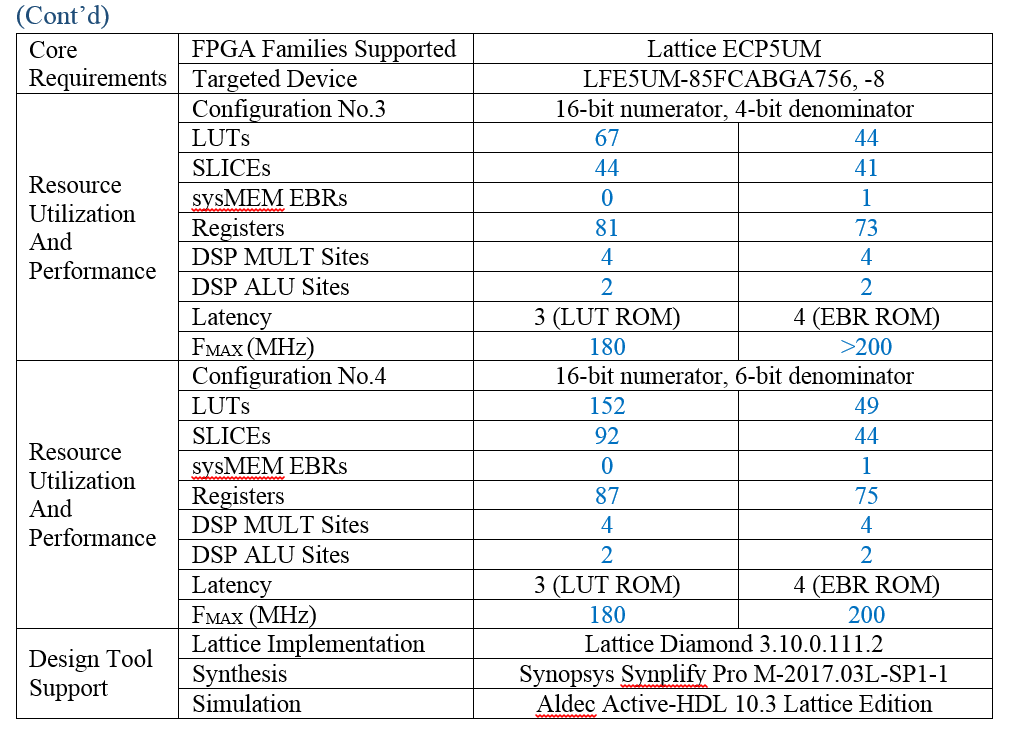

目前初步实现了DIV_32_4, DIV_32_6, DIV_16_4, 和DIV_16_6四种模式,具体实现效果如下:

实现起来很简单,就不共享源码了,如果有兴趣地可以联系我索取(PS,自己写一下也花不了多长时间)。