Lattice Video Frame Buffer IP调试笔记

1赞最近几天在Lattice的EVDK开发板上验证调试了Video Frame Buffer的IP,期间遇到一些问题,在大牛的帮助下,终于解决了,今天来分析总结一下。

1、Lattice Video Frame Buffer IP简单介绍

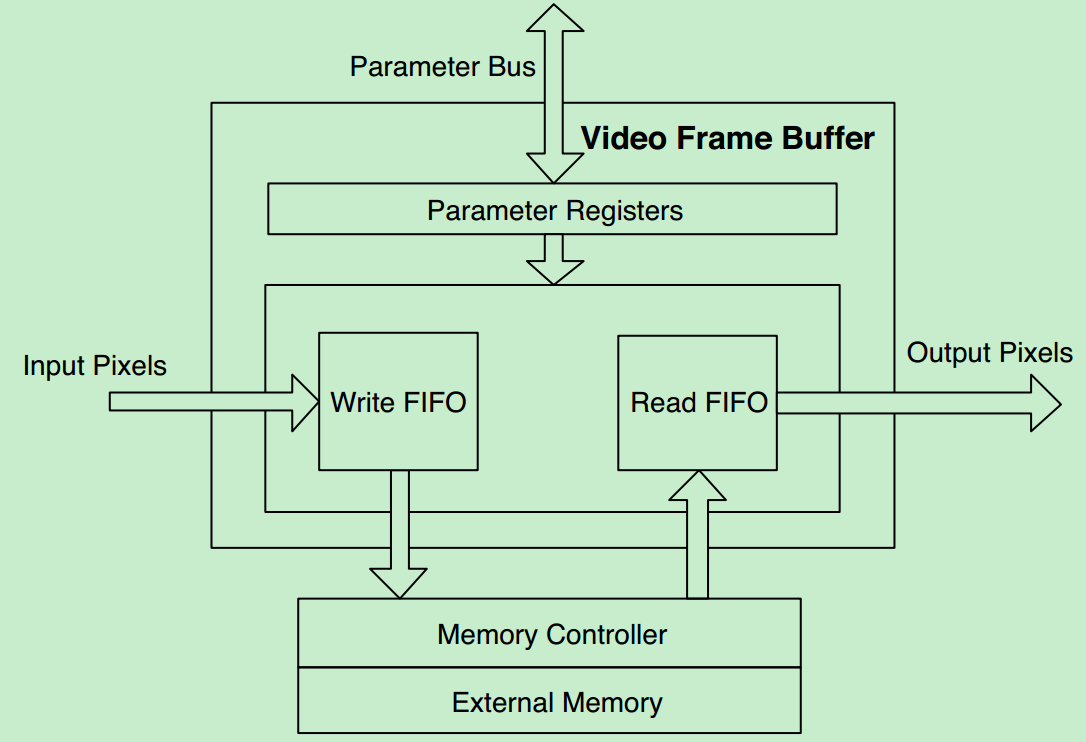

Lattice Video Frame Buffer(下面简称VFB IP)是一个将外部存储期间作为缓存的,且支持帧率转换和多种格式的视频帧缓存IP。

其主要特点如下:

• Supports single color, YCbCr 4:2:2, YcbCr 4:4:4/RGB video formats • Supports input and output resolutions of 64 x 64 to 4K x 4K pixels • Supports serial and parallel pixel processing • Supports frame rate conversion • Supports dynamic parameter update of frame size and Keep mode • Supports configurable parameter bus width • Supports configurable parameter bus clock • Supports configurable memory bus width and base address • Supports configurable memory burst length and burst count • Configurable internal FIFO type and depth • Supports 8, 10 or 12-bit color depth per plane

其中,帧率转换的功能比较“鸡肋”,比如,30p到60p转换就是把每一帧都重复一遍,60p到30p就是丢掉一帧……目前来说支持ECP3、ECP5和XP2系列的器件,VFB IP的功能框图如下:

其中,支持的外部存储有DDR2(ECP3)和DDR3(ECP3和ECP5),VFB IP的IO框图如下:

总的来说,该IP的使用难度还是比较低的,时序控制也不是很复杂,但是也有一些细节需要注意,否则可能会浪费比较多的时间Debug……

2、调试中遇到的问题与解决方案

调试的过程中,主要遇到一个问题,就是VFB IP往DDR3 MC IP写的时序都是正常的,读的时序也是正常的,但是就是读的数据不对……这里说的不对只是数据的位置不对,但是数据的值确实正确的。输出到显示器上的表现就是画面乱掉了,如果发送的数据时ColorBar的话,则表现为行里面的数据乱掉了,后面的数据可能会到前面,前面的数据可能会到后面。

但是图像显示还是很稳定的,包括dvalid_out信号和frmsync_out信号都是稳定的。初步分析,感觉很有可能是读写地址给的不正确。关于读写地址,在VFB IP的文档中(见附录)有这样一段话:

The video frame buffer assumes a memory byte addressing scheme. When connecting the memory controller, the address connection should be adjusted according to the DDR memory data width.

Normally the address connection can be (Assuming the DDR2/3 memory has 27 bits address width):

ddr_addr = {1’b0,mem_addr[25:0]}; // for 8-bit DDR memory only

ddr_addr = {2'b00,mem_addr[25:1]}; // for 16-bit DDR memory only

ddr_addr = {3'b000,mem_addr[25:2]}; // for 32-bit DDR memory only起初,我理解上面注释中的32-bit为DDR3 Memory的DW,因为我用了两个x16 Configuration的DDR3颗粒,所以DW应该是32,所以:

assign ddr_addr = {3'b000,mem_addr[25:2]};但是怎么调试都不对,然后我又把它理解为是DDR3 MC IP那边的位宽,也就是128-bit,于是:

assign ddr_addr = {5'b00000,mem_addr[25:4]};可是还是不对……后来在大牛的指导下,直接改为:

assign ddr_addr = {1’b0,mem_addr[25:0]};居然好了……

至于VFB IP的文档中为什么要写那段话,就不得而知了……(如果哪一天搞明白了,会第一时间回来更新的)

3、该IP使用注意事项

3.1、VFB IP的frmsync_in信号比较特殊,其要求必须在每一帧图像的第一个有效像素点上(且只能持续一个像素时钟周期);

3.2、如发现VFB IP的ready信号不连续(或者是只向DDR中写数据,不从DDR中读数据……),则很有可能是Write FIFO的深度不够(建议刚开始调试的时候可以直接把深度给到最大),如下图所示:

正确的ready信号如下图所示:

3.3、当使用的是DDR3 Memory的时候,VFB IP的BL应该与DDR MC IP保持一致(建议使用BL8 提高效率),而VFB IP的CMD Burst Cnt则应为DDR MC IP的一半;当使用的是DDR2 Memory的时候,BL和CMD Burst Cnt则都应相等。

3.4、在配置DDR MC IP的时候,一定要将Data_rdy to Write Data Delay设置为2(默认值是1),否则frmsync_out信号可能会不正常!

3.5、注意DDR MC IP和VFB IP之间的地址映射问题,如本文第二部分所述。

3.6、如果输出像素时钟iclk和输出像素时钟oclk不相同时,应注意frmsync_out信号是否异常(建议iclk和oclk的频率为整数倍关系)。

3.7、建议在VFB IP之后再加一个行Buffer(用FIFO即可实现),如果用户发现自己的设计中,发现dvalid_out信号不连续,则必须要使用行Buffer!