AMBA学习笔记——APB总线与APB桥详解

0赞APB 的全称为Advanced Peripheral Bus。AMBA 中的 APB 总线主要用在低速且低功率消耗的外设。在 APB 总线中,唯一的主机为APB桥(比如AHB2APB桥),其它一些低速和低功率的外围皆为从机。因此 APB 总线不需要类似于AHB中的仲裁器等功能,也就是说APB总线的整个架构较AHB要简单许多。

为了使APB容易被整合进大部分的设计流程中, AMBA Spec规定APB所有信号必须在时钟上升沿触发时进行传递。这样的设计方式可改善高速电路的效率,且EDA对这种设计方式的处理技术较为成熟且容易实现,便于静态时序分析和测试。

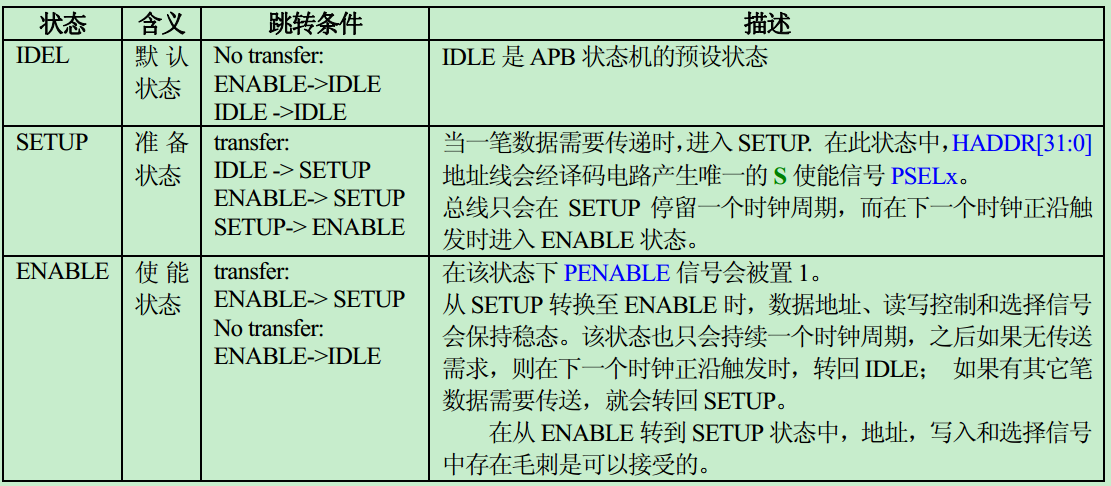

APB的状态机如下图所示:

从状态机看,APB 对每一笔数据的传送,均需花 2 个周期的时间,显然APB的数据传递方式并不适用在有流水线架构(Pipeline)的模块设计中。

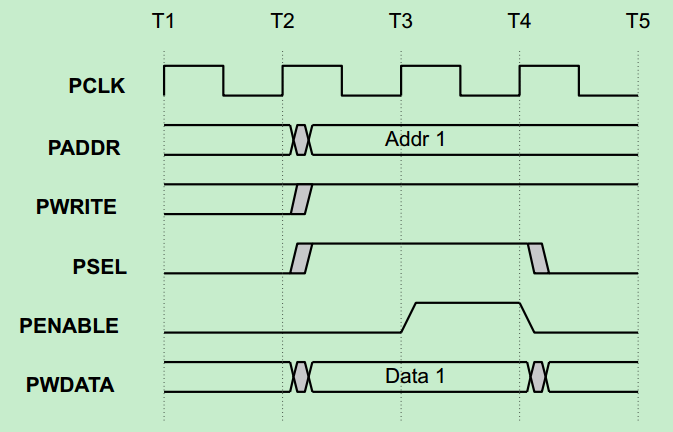

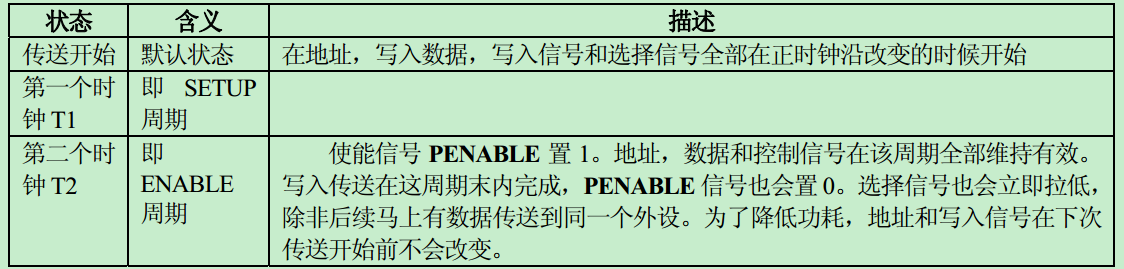

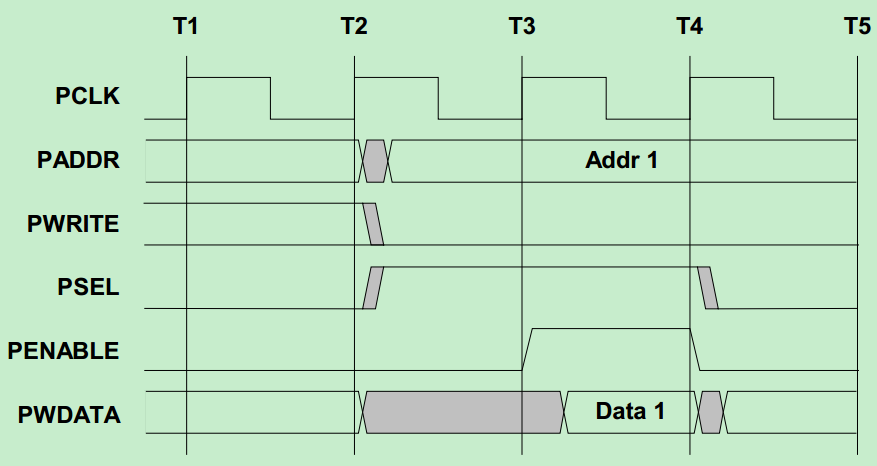

下图为 APB 基本的写数据传送时序:

以下简单介绍它的运作情形。在 T1 时,状态机进入预设的 IDLE 状态;

在 T2 时,主机会在时钟上升沿触发时,更新需要操作的数据地址、读写控制信号和待写入的数据,这个周期也就是刚才所提及的SETUP状态。译码电路在此状态会根据地址去译码出所要写入的APB从机,此时所对应的从机的 PSEL 信号也将由 0 变 1;

在 T3 时,有限状态机会进入 ENABLE 状态, PENABLE 信号在此状态会被设成 1;

在 T4 频率正沿触发时, PENABLE 信号将由 1 变 0,而 PSEL 信号在若没有其它数据的写入动作时,也将由 1 变 0。为了减少功率的消耗, APB 的数据地址和读写控制信号在下一笔数据传递前,将不会作任何改变。

注:协议要求使能信号要干净,但是在连续的传输中PSEL和PENABLE信号可能会有毛刺。

下图为 APB 进行读取数据动作的时序图:

由图中可发现除了PWRITE信号变成了低电平表示读操作之外,APB读操作时序图和写操作时序图非常相似,在这里我们就不再作详细的解释。

要特别注意的是,在T3后,也就是在进入ENABLE周期后,APB从必须要将主机所要读取的数据准备好,以便主机可以在T4 时钟上升沿,正确的将数据读取。

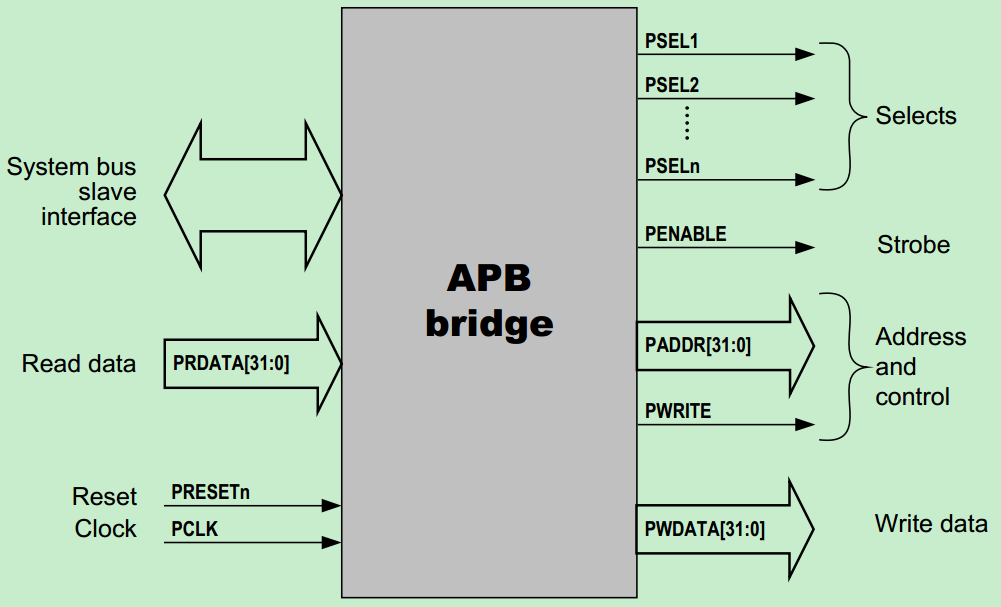

APB的各个组件示意图如下所示: