PCIe扫盲——128/130b编码详解

2赞连载目录篇:http://blog.chinaaet.com/justlxy/p/5100061871

前面的文章介绍过PCIe的Gen1和Gen2模式下,物理层使用的是8b/10b的编码。这种编码方式能够实现直流均衡,并且能将数据流中的连0连1控制在5个以内(最多5个连续的1或者0),从而可以降低物理层CDR设计的复杂度。但是8b/10b编码的缺点也很明显:浪费了20%的带宽资源,以PCIe Gen2为例,5GT/s的速率却只有4Gbps的带宽。

注:PCIe的真实带宽还受到TLP包中的非数据内容,DLLP和Ordered Sets,甚至Root端的驱动和应用程序的影响。具体可以参考之前的文章:http://blog.chinaaet.com/justlxy/p/5100062236

本文将简要地介绍PCIe Gen3及以上版本中所使用的128b/130b编码技术。128b/130b编码是以太网中使用的64b/66b的演进版本,关于64b/66b,可以参考:http://blog.chinaaet.com/justlxy/p/5100064750

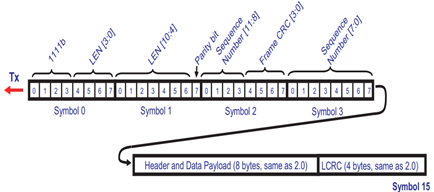

128b/130b相比于8b/10b,在带宽利用率上有了显著地提升,从80%到98.46%。在评估总线性能的时候,甚至可以忽略不计。与以太网中使用的64b/66b类似,128b/130b编码是在128 bit的Payload前面加上了2 bit的同步头,如下图所示:

该同步头(Sync)为01b时,表示其后面跟的是Ordered Set;为10b是,则表示其后面跟的为非Ordered Set数据。需要注意的是,Byte Striping逻辑会将同步头在每一个Lane上重复(如果有的话,即非x1模式),以便于接收端识别同步头。我们将这2bit的同步头和128bit的Payload,一起称为数据块(Data Block)。在Gen1/2模式下,物理层首先完成位锁定(Bit Lock),然后尝试去完成字节锁定(Byte Lock)。而在Gen3(以及以上版本),物理层完成位锁定之后,会尝试进行块锁定(Block Lock,与Gen1/2的字节锁定对应,Gen3中并没有字节锁定的概念)。

注:当然,完成块锁定需要借助特定的数据流,在PCIe中使用的00h和FFh交替的数据流,即EIEOS(Ordered Set的一种)。

PCIe一共定义了5种类型的Ordered Set:

※ TS1 and TS2 Ordered Set (TS1OS/TS2OS) :用于链路初始化和训练

※ Electrical Idle Ordered Set (EIOS) :用于电气空闲状态

※ FTS Ordered Set (FTSOS) :用于L0s状态到L0状态的切换

※ SKP Ordered Set (SOS) :用于CTC(Clock Tolerance Compensation)

※ Electrical Idle Exit Ordered Set (EIEOS) :V2.0 Spec增加的

※ Start of Data Stream Ordered Set(SDS):仅适用于Gen3及以上版本,当链路准备发送数据流时,会先发送SDS,然后进入L0状态。

需要注意的是,与发送有效数据流(非Ordered Set)不同,发送Ordered Set时,所有的内容都需要在同一时刻在所有的Lane上(如果有的话)同时发送。以FTS为例,如下图所示:

注:几乎所有的Ordered Set的Payload的都是16个字节,但是有一个例外:SOS(SKP Ordered Set),其Payload可以是8,12,16,20或者24个字节。

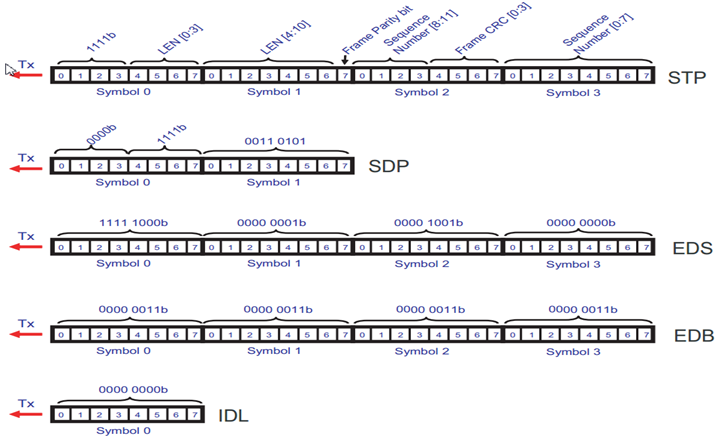

对于同步头为10b(即非Ordered Set)时,还需要借助Tokens(Gen3及以上版本才有的概念)来区分Payload中的数据的类型是TLP还是DLLP。PCIe Spec一共定义了5种数据结构(即5种Tokens):

※ Start TLP (STP) — followed by a TLP

※ Start DLLP (SDP) — followed by a DLLP

※ Logical Idle (IDLA) — sent when there is no packet activity

※ End of Data Stream (EDS) — Precedes the transition to Ordered Sets

※ End Bad (EDB) — reports a nullified packet has been detected

每种Token的结构如下图所示:

以STP为例:

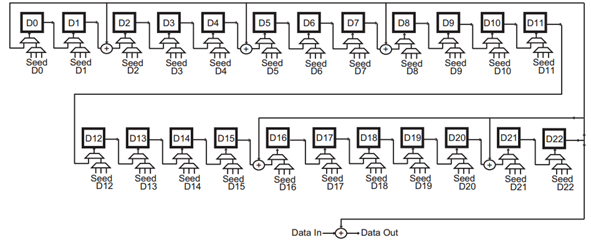

有人可能有疑问了,128b/130b编码之所在128bit的Payload前面增加了2bit的同步头,严格意义上都不能称之为编码。显然仅仅依靠128b/130b编码根本不可能实现8b/10b编码那样的直流均衡,因为Gen3使用了全新的扰码方式,以达到直流均衡的目标。Gen3的扰码算术表达式如下:

G(x)=x^23+x^21+x^16+x^8+x^5+x^2+1

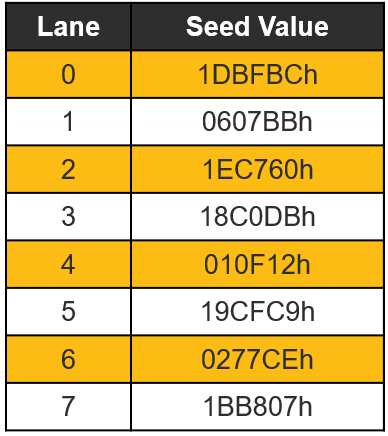

为了减少各个相邻的Lane之间的干扰,每个Lane使用的扰码种子是不同的,如下表所示:

注:对于x16/x32的应用而言,可以依次重复使用各个Lane的种子,即Lane 8继续使用Lane 0的值,Lane 9使用Lane 1的值,依次类推。

注:与以太网中使用的64b/66b编码类似,128b/130b无法像8b/10b编码那样将连续的0(或者连续的1)限制在较小的范围之内,理论上,128b/130b可能出现的最大的连续0(或者连续1)可以达到128(最坏的情况下)。128b/130b编码只能借助扰码来实现较长时间内的直流均衡。这也是为什么PCIe Gen3的速率仅仅比Gen2的物理传输速率提高了3GT/s,其物理层(主要是CDR)的设计复杂度却增加了很多很多的原因。

注:2bit的同步头不会被扰码,当发送/接收到EIEOS或者FTSOS后,扰码器会重新初始化。除了TS1OS和TS2OS之外的所有的Ordered Set的所有Symbol都不会被扰码,TS1OS和TS2OS的Symbol0不会被扰码,Symbol 1~13会被扰码,而Symbol 14~15是否被扰码取决于扰码器判断扰码或者不扰码,谁更有利于直流均衡。