ALTERA Qsys中PCI-E IP硬核的使用

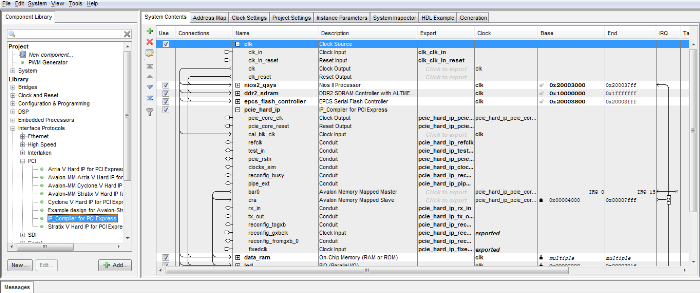

0赞首先打开Qsys,如下图:

点击Qsys中的PCI下的IP_Compile for PCI Express,或者直接搜索。

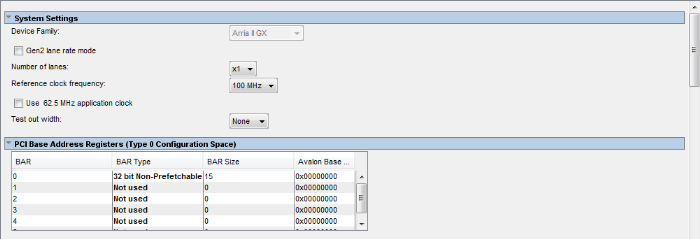

接下来就是一些重要的设置,下面逐一解释:

Device Family即器件。根据不同的器件选择即可。

Number of lanes即FPGA与外部收发数据所用的通道数,对应的RTL例化将会生成一组tx和rx的串行数据通道。

Reference Clock Frequency:输出到PCI总线的工作时钟。

Test out width: 测试用,可以不选。

PCI Base Address Register:基址寄存器,由PCI总线转换到Avalon总线后Avalon总线上需要连接的外设的地址空间,根据不同的外设需求选择BAR Size,即地址宽度,以及多个BAR。因为Avalon总线是32bit,最大寻址空间是4GB,转换到PCI-E总线是按页的方式。

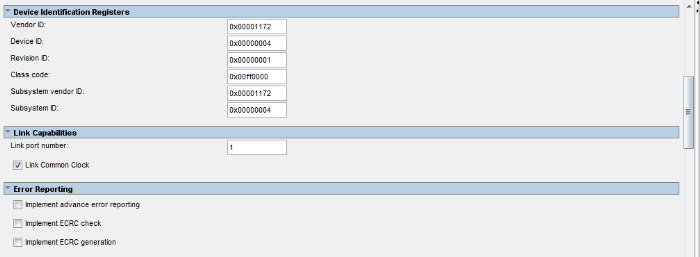

以上Vendor ID等是在PCI-E总线上注册Avalon总线及设备时所需,保持默认即可。

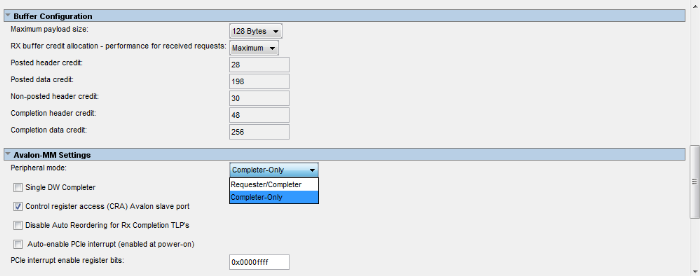

上面设置的是数据缓存的大小,根据需求设置即可。

Periph mode:这里选择的是Completer-Only,也就是PCI-E端的CPU等为主设备,可以对Avalon上的设备进行读写请求,接受中断。如果选择的是Requester/Completer,这样既可以对Avalon上的设备进行读写请求,接受中断,也可以Avalon总线上的设备发出对PCI-E端数据包的读写请求。

CRA:控制寄存器,这里包含了一些桥接的寄存器信息,即Bridge Registers。如果选用PCI-E端读写这个寄存器,那么只要cra端口直接连接到bar0即可,当然也可以在Avalon总线段对其设置。

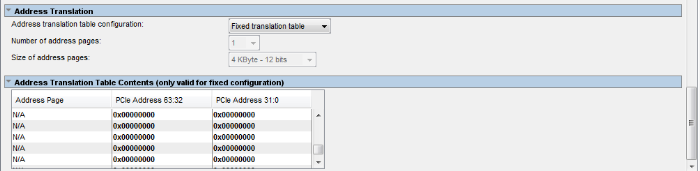

上图是地址转换的相关设置,如果使用者想随时调整转换地址空间的页表,选择Dynamic translation table,下面设置的是页表个数和大小。一般如果希望地址空间分配是固定的,选择Fixed translation table即可。

上图是地址转换的相关设置,如果使用者想随时调整转换地址空间的页表,选择Dynamic translation table,下面设置的是页表个数和大小。一般如果希望地址空间分配是固定的,选择Fixed translation table即可。

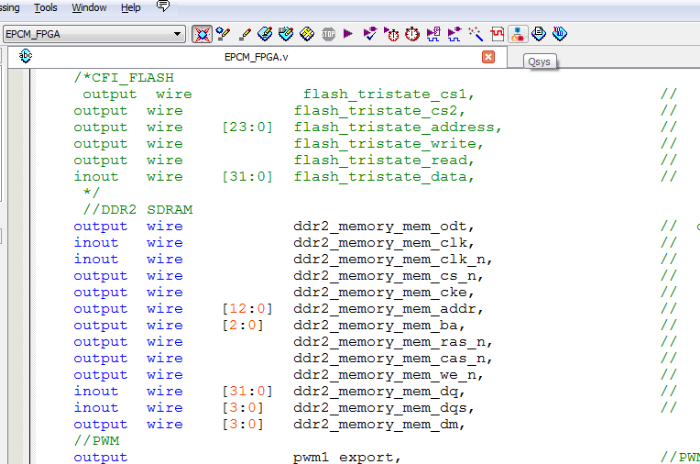

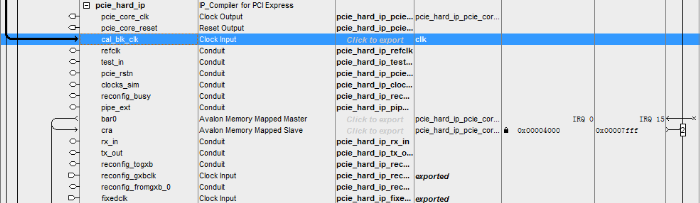

需要输入、输出的端口如下图:

需要连接Avalon的外设连接在bar0即可。cal_blk_clk连接到Avalon总线的时钟。

这样,就可以编译出RTL代码了。

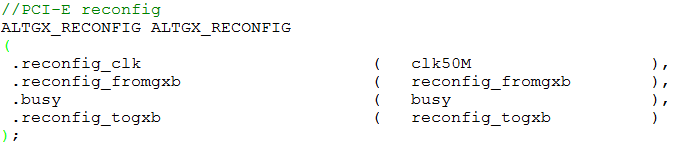

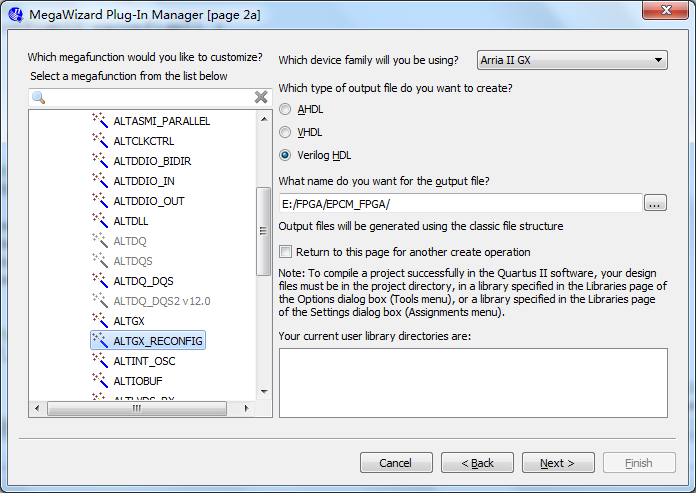

这里需要注意的是,对于Arria II GX FPGA,提供给PCI-E PLL时钟应该使用ALTGX_RECONFIG

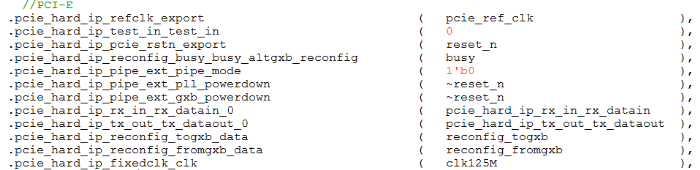

例化如下: