【原创】Allegro SI 高速信号完整性仿真连载之三(附详细流程)

4赞 前面两节对Allegro SI信号仿真的各项条件进行了介绍,下面将结合具体例子来说明如何来仿真。如图所示一个预布局好的PCB,以下将对PCB中一对差分信号进行仿真,

首先必须进行阻抗控制,器件模型分配,前面已经讲过具体的操作过程,这里不再赘述,接下来我们需要对差分对进行拓扑提取。

1、设置互联模型参数

从Allegro PCB SI GXL窗口选择Analyze---SI/EMI Sim---Preference命令,弹出Analyze Preferences窗口,选择“Interconnect Models”如下图:

在“Unrouted Interconnect Models”部分,设置“Percent Manhattan”为100,“Default Diff-Impedance”为100ohm,在“Topology Extraction”部分确保选择“Differential Extraction Mode”,如果没有选择,差分对拓扑将仅使用理想传输线模型。为了使用理想的耦合传输线模型,必须选择“Differential Extraction Mode”。

2、提取拓扑

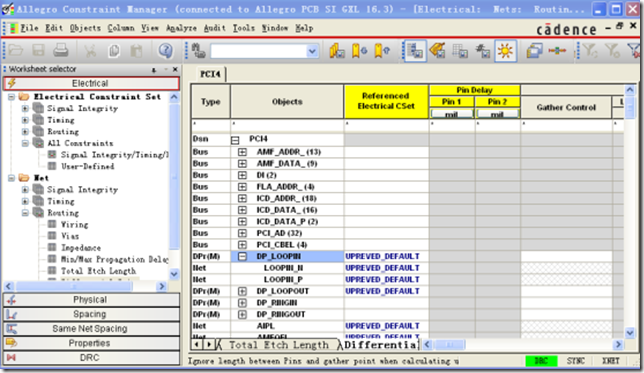

在“Allegro Constraint Manager”窗口选择“Net”---“Routing”---“Differential Pair”如下图:

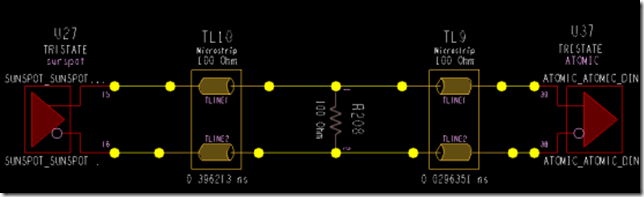

选择“DP_LOOPIN”差分对(差分对可以在原理图或者导入PCB之后设置),单击右键,选择“SigXplorer”命令,弹出“SigXplorer PCB SI GXL”窗口,显示了提取的有理想耦合的传输线模型的差分对拓扑,如下图所示:

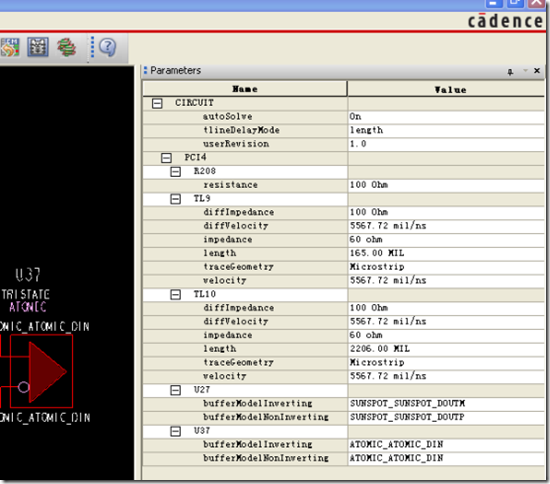

在窗口的右侧有一个“Parameters”设置表格,为了直观,可以把“tlineDelayMode”的“time”改为“length”。保存拓扑结构。

3、分析差分对网络:

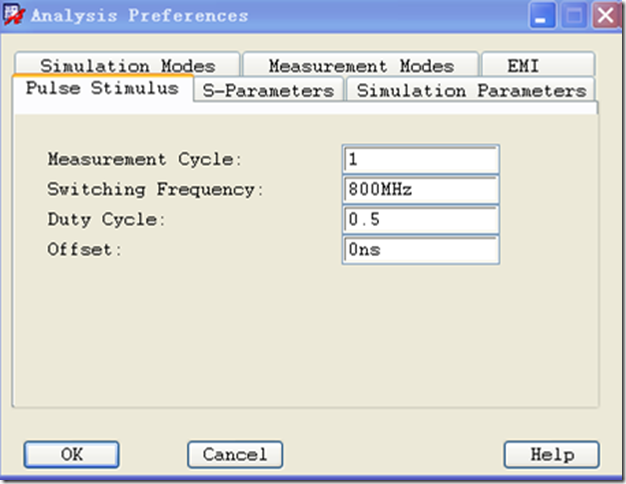

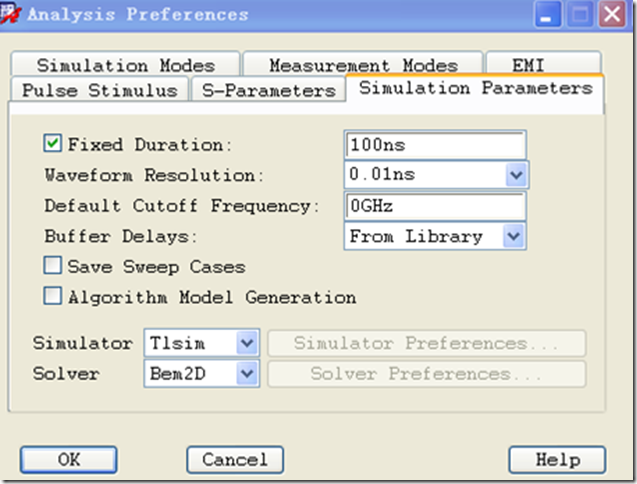

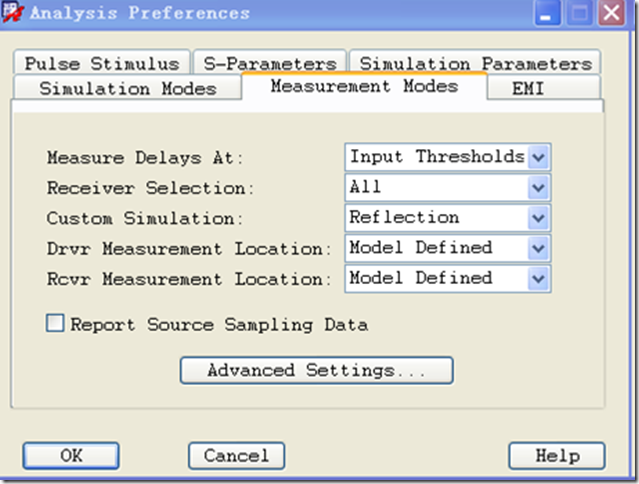

选择“Analyze”---“Preference”选项,弹出“Analyze Preference”窗口,设置“Pulse Stimulus”(记录参数)、“Simulation Parameters”(仿真参数)、“Simulation Modes”(仿真模式)和“Measurement Modes”(测量模式),如下图:

Measurement Cycle:设置仿真器在第几个周期进行参数测量。一般情况下,由于驱动器的瞬态效应,我们对于时钟信号从第三个周期进行测量,对于其它的信号从第一个周期进行测量。

Switching Frequency:开关频率或称为脉冲频率。该值决定了在设置激励源为PULSE 时所使用的频率值,该值我们通常设置时钟的频率。

Duty Cycle:占空比,缺省设置为0.5。

Offset:脉冲偏移量,用来控制主网络驱动器与相邻网络驱动器之间的激励时间差。如果该值为正,则相邻网络驱动器在主网络驱动器之后产生激励。

Fixed Duration:指定仿真的持续时间长度。如果这个值未确定,则仿真器动态的为每一次仿真选择时长。当该值确定时,仿真运行的时间就为该项中所确定的固定时间长度。这项值的大小与波形文件的大小成正比。如果我们需要仿真的是2M 信号,一个周期应该是500ns(τ=1/f=1/2x106=5x10-7s=500ns),所以我们设成600ns,表示一个周期多一点。

Waveform Resolution:波形分辨率,决定仿真过程中产生波形的采样数据点的多少。使用Default 时,分辨率为传输线长的1/100。通常我们要求分辨率为最短传输线的1/10。

Cutoff Frequency:表明互连线寄生参数提取所适应的频率范围,缺省为0GHz。在对IBIS 的PACKEG等寄生参数进行RLGC 矩阵提取时,为了不考虑频率的影响将截止频率设为0,此时的矩阵不依赖于频率,并且提取速度较快,但精度稍差。当设置了截止频率后,RLGC 矩阵将是综合矩阵,它将基于频率的参数影响,考虑了频率参数影响的RLGC 矩阵具有较高的精度,但提取速度较慢。如果对该值设置,一般建议设置该值不要超过时钟频率的三倍。如果没有特殊要求通常设置为0 即可。

Buffer Delays:缓冲器延时选择。缓冲器延时有两种选择:On-the-fly 和From library。On-the-fly 是根据测试负载的参数计算出Buffer Delay 曲线,From library 是从库中获取。在实际应用时,我们均是通过器件的DATASHEET 查出测试条件由软件自动计算出Buffer Delay 曲线,因此,这项值的内容通常设为On-the-fly。

Save Sweep Cases:当选择时指明保存仿真波形和环境数据。

Simulator:选择仿真器,包括Tlsim 和Hspice 两种,一般选择Tlsim。

Measure Delays At:延时测量的参考点,有两种选择:Input Thresholds(输入门限值)和Vmeas 表示以输出Buffer 的参考电压进行测量的。通常选择Input Thresholds。

Receiver Selection:接收器选择。有两种选择:All(表示所有非驱动的器件都作为接收)和Select One(在仿真开始时它会让你选择其中的一个作为接收源)。根据需要选择,通常选择All。

Custom Simulation:仿真内容。包括:Reflection(反射仿真)、Crosstalk(串扰仿真)和EMI(电磁干扰仿真)。

Report Source Sampling Data:确定是否报告源采样数据。

4、SigXplorer 中的仿真过程:

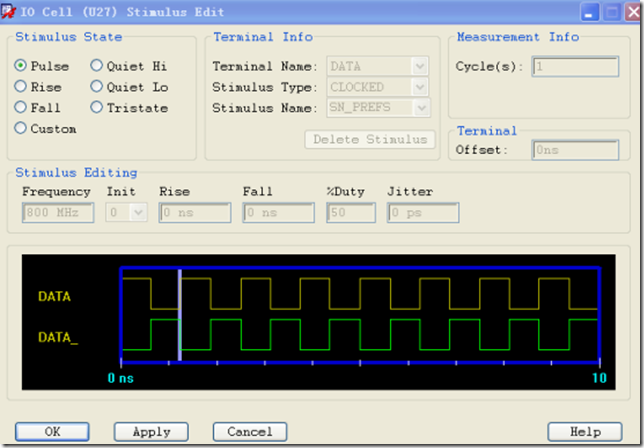

在发送端IOCell模型的TRISTATE上点击一下,在弹出的下面窗口中选择Pulse选项:

Pulse:表示激励信号为连续脉冲方波,就是时钟源性质的波形,如果选择Pulse,整个界面

中的其他选项是灰的,不允许再选。

Rise:表示激励信号为上升沿。

Fall:表示激励信号为下降沿。

Quiet Hi:表示激励信号为恒高。

Quiet Lo:表示激励信号为恒低。

Custom:表示激励信号由该界面中的参数定制,此时界面中的其它参数将可设定。

Tristate:表示三态。通常接收端设为该状态。

其它组合框只有在Custom状态时可用。一般对于干扰源选择pulse,rise,fall;被干扰对象:选择QuiteHi,Quite Lo;接收器选择Tristate。

Terminal Name:表示仿真信号的类型有Data和Enable两种。Data为要仿真的数据信号,Enable为使能信号,当Enable为高时,仿真有效;当为低时,为激励源断开终端时的仿真结果。

Stimulus Type:表示激励类型。

Stimulus Name:取的激励信号名。

Cycle(s):表示在第几个周期测量数据。

Offset:仿真信号相对于时钟的延时。

该框设置时钟信号的频率(Frequency)、样式(Pattern)和抖动(Jitter)。

在SigXplorer 窗口最底端选择Measurements 标签,点击Reflection 前面的“+”号打开测量反射参数的列表,在弹出菜单中选择需要测量的反射参数。选择菜单File=》Save,保存一下拓朴模型。

与反射相关的参数简介:

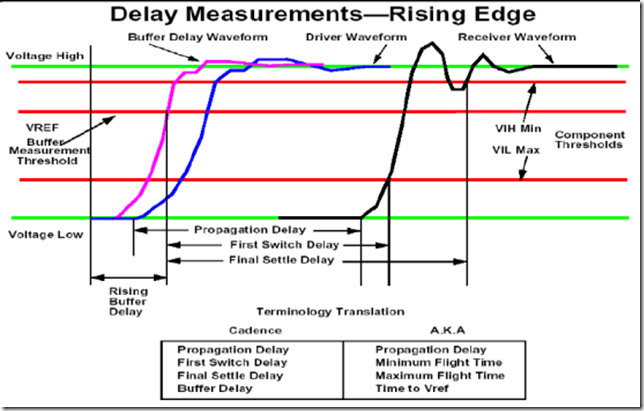

BufferDelayFall:如图(1)所示。就是BufferDelay 曲线从高电平下降到测量电压值Vmeas 时的延时值。BufferDelay曲线是软件根据模型库中测试负载参数计算得到的,测试负载参数必须根据器件的DATASHEET手册得到,不能使用IBIS模型文件中缺省参数,原因是我们在进行时序分析时器件的各种延时参考数据都是从DATASHEET中得到,而该数据是以DATASHEET 中的测试负载为依据的。

BufferDelayRise:如图(2)所示。就是BufferDelay 曲线从低电平上升到测量电压值时的延时值。

FirstIncidentFall:第一次开关下降时间。

FirstIncidentRise:第一次开关上升时间。

Monotonic:输入波形的单调性检查,如果上升或下降沿中有非单调性现象,则检查结果为False。

MonotonicFall:输入波形上升沿的单调性检查。

MonotonicRise:输入波形下降沿的单调性检查。

NoiseMargin:噪声容限。如图(4)所示。该值在Result中报告的是NoiseMarginHigh和

NoiseMarginLow中的最小值。

NoiseMarginHigh:高电平噪声容限。是从VIH Min 到超过Vin Min 电压后震荡波形的最低点的电压差。

NoiseMarginLow:低电平噪声容限。是从VIL Max 到低于VIL Max 电压后震荡波形的最高点的电压差。

OvershootHigh:高电平过冲。如图(4)所示。以0V为参考点,上升波形的最高点电压值。

OvershootLow:低电平过冲。如图(4)所示。以0V为参考点,下降波形的最低点电压值。

PropDelay:如图(2)所示。它是传输线的传输延时值。

SettleDelay:是SettleDelayFall 和SettleDelayRise 两者的最大值。

SettleDelayFall:如图(1)所示。它是从BufferDelay 下降沿的Vmeas 点开始到接收波形下降曲线

最后一次穿过低电平阈值时的延时值。

SettleDelayRise:如图(2)所示。它是从BufferDelay 上升沿的Vmeas 点开始到接收波形上升曲线最后一次穿过高电平阈值时的延时值。

SwitchDelay:是SwitchDelayFall 和SwitchDelayRise 两者的最小值。

SwitchDelayFall:如图(1)所示。它是从BufferDelay 下降沿的Vmeas 点开始到接收波形下降曲线第一次穿过高电平阈值时的延时值。

SwitchDelayRise:如图(2)所示。它是从BufferDelay 上升沿的Vmeas 点开始到接收波形上升曲线第一次穿过低电平阈值时的延时值。

以上参数中,Monotonic、MonotonicFall、MonotonicRise、NoiseMargin、NoiseMarginHigh、

NoiseMarginLow、OvershootHigh、OvershootLow 与信号完整性有关,其它的与时序仿真有关。

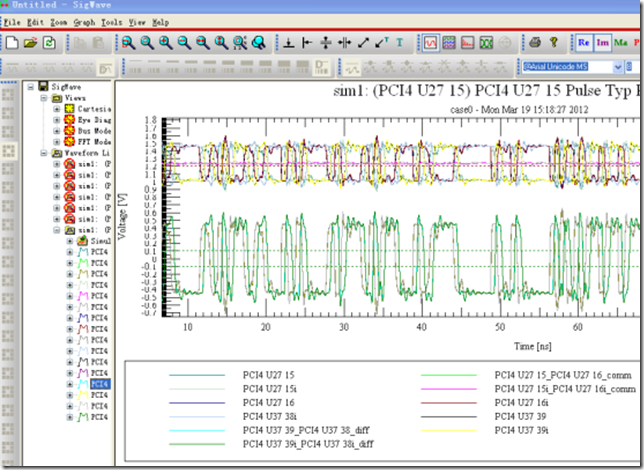

执行“Analyze”---“Simulate”,弹出仿真波形如下:

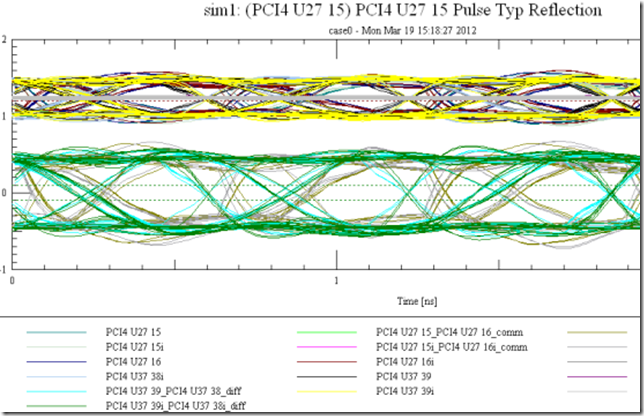

从“SigWave”菜单中选择“Graph”---“Eye Diagram Mode”命令---波形的眼图如下所示:

5、应用差分对约束:

当以上仿真图形比较理想时,可以将拓扑约束应用到PCB设计。具体方法如下:

在“Constraint Manager”窗口中选择“File”---“Import”---“Electrical Csets”命令,弹出“Import Electrical Csets”窗口,将之前保存的拓扑文件加入。

选择之前的差分对“DIFFLOOPIN”后面的“Referenced Electrical CSet”表格,弹出“Elecreical CSet Reference”对话框,选择之前保存的拓扑约束。

接下来就可以对差分线进行布线了,如果布线违反了约束规则,就会出现DRC错误。

说明: 由于本人能力有限,博文上有不正确的地方欢迎批评指正,另外也可加QQ群进行讨论:中国硬件设计交流PCB&SI 217166793。