FPGA的DDR2 SDRAM IP核的使用

1赞

DDR2 SDRAM 作为高速大容量存储器件,非常普遍的应用在我们的工程中。在FPGA外挂DDR2 SDRAM,如果我们直接编写驱动逻辑,是非常麻烦而且耗时的事情,但是Altera在开发环境中给我们提供了这样的IP核,大大简化了我们的开发周期。下面将介绍DDR2 SDRAM IP核的使用过程。

DDR常见类型:

SDR SDRAM :Single Data Rate。工作电压:3.3V

DDR SDRAM :Double Data Rate。2bit预读,工作电压:2.5V

DDR2 SDRAM :4bit预读,工作电压:1.8V

DDR3 SDRAM :8bit预读,工作电压:1.5V

SDR和DDR均采用单端时钟信号,DDR2和DDR3采用差分时钟作为同步时钟。

DDR在时钟的上升沿和下降沿各传输一次数据,这使得DDR的数据传输速率为传统SDRAM的两倍。

DDR2上电初始化过程:

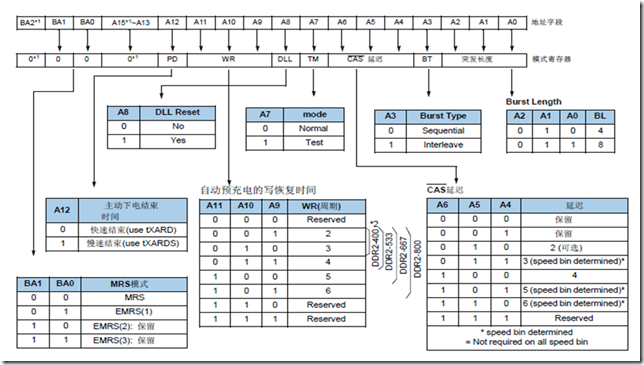

MRS(模式寄存器):

EMRS(1)(扩展模式寄存器)

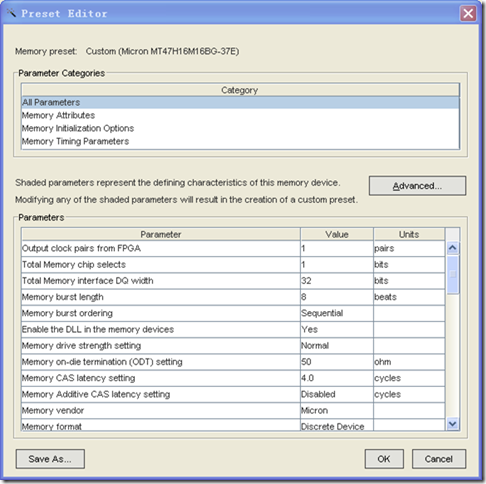

DDR2 IP核的生成:

Full rate controllers:

For one chip select: width = row bits + bank bits + column bits – 1

For multiple chip selects: width = chip bits + row bits + bank bits + column bits – 1

HALF RATE CONTROLLERS:

FOR ONE CHIP SELECT: WIDTH = ROW BITS + BANK BITS + COLUMN BITS – 2

FOR MULTIPLE CHIP SELECTS: WIDTH = CHIP BITS + ROW BITS + BANK BITS + COLUMN

BITS – 2

用户侧接口信号 | 与DDR2物理连接的信号 |

local_address[22:0] local_write_req local_read_req local_burstbegin local_wdata[127:0] local_rdata [127:0] local_be[15:0] local_size[2:0] pll_ref_clk local_ready local_rdata_valid local_init_done | mem_odt mem_cs_n mem_cke; mem_addr[12:0] mem_ba[2:0] mem_ras_n mem_cas_n mem_we_n mem_dm[3:0] phy_clk mem_clk mem_clk_n mem_dq [31:0] mem_dqs[3:0] |