03 环境约束

0赞

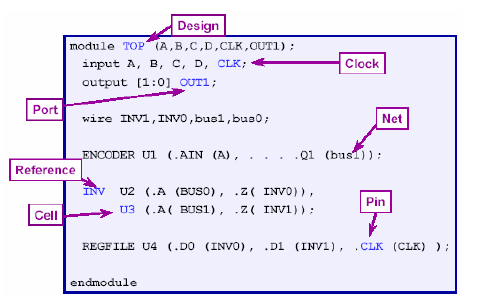

上面所说的port为DC中六大object之一,design、clock、port、cell、pin、net。

Design:设计名称,理解为***.v中的***;

Clock:时钟;

Port:design的input,output;

Cell:design中调用的模块或低一层design;

Pin:例化cell的输入输出

Net:cell间内部互联线

//从上面描述可知 design和cell有时候可以相互转换。

PVT设置:

工艺、电压、温度。这些情况一般只考虑最差ss和最好ff。只考虑setup可以测ss,只考虑hold 可以测ff。如果setup文件只读入了一个target_library那么只有一个工作条件,可以不用做这一步。如果读入多个仍需设置。

Set_operating_conditions –max “ ss***”/

\-min “fast***”

线负载模型:

Set_wire_load_mode enclosed | top | segmented

set_wire_losd_model #跟工艺厂多沟通获取具体值

Top:所有层次子模块的wire_load和top-level相同,如果用户计划flatten设计去layout可选择此模式编译子模块;Enclosed:子模块net的wire_load和enclosed 它的最小模块相同,推荐用于在layout后logical and physical hierarchy相似的设计;Segmented:子模块之间net的wire_load和enclosed该net的模块相同,需技术库提供Segmented wire_load,一般不常用;wire_load模型的选择很重要也可以让DC自己设置 set auto_wire_load_selection false

驱动:

如果不对工程进行输入驱动,DC默认无穷大即,translation time为0。

set_driving_cell –lib_cell inv1 [get_ports A] #这句命令是将port A的输入驱动模拟成cell inv1输出脚连接。

set_driving_cell –lib_cell FD1 –pin Q [get_ports B]#这句命令是将port B的输入驱动模拟成cell FD1的Q脚连接。这句话对比上面那句是因为FD1除了Q还有一个Q’的输出。要固定其哪一个输出模拟接到B。如果不加pin,DC将默认使用找到的第一个引脚

set_driving_cell -library $lib_name -lib_cell inv1 [all_inputs] #此命令是让所有input的输入驱动为前面所定义的lib_name中的inv1 cell。

set_driving_cell [expr [load_of $lib_name/an02d0/A1] * 15] [all_inputs] #均是假想一个驱动单元在输入端口之前,据此单元计算。

负载电容:

默认为0,但是太过于乐观。同样如果设置太大又会增加translation time进而影响性能。

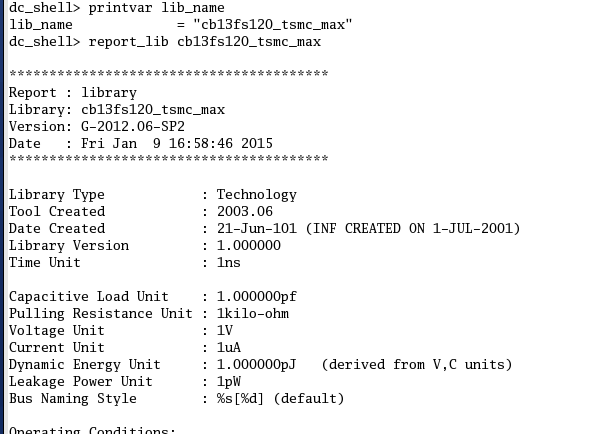

set_load 5 [get_ports OUT1] #设置OUT1为5pf,输出负载默认为pf也可report_lib查看单位。

set_load [load lib_name/ an01d0/A1] [get_ports OUT2]

set_load [expr [load_of $lib_name/an01d0/A1] * 15] [get_ports OUT3] #这个是使OUT3输出负载为定义的lib_name中an01d0的A1脚的负载电容15倍。

负载预算:load bugeting

如果输出电容负载不清楚,采用此办法。

Conservative Output Load Algorithm

Used for “load budgeting” if actual output load values are

not known. Finds the largest max_capacitance value

in the library and applies that value as a conservative

output load

set LIBJslAME ssc_core_slow

set MAX_CAP 0

set OUTPUTJ^INS [getjib__pins $LIBJMAME/7* \

-filter "direction == 2"]

foreachJn_collection pin $OUTPUT_PINS {

set NEW__CAP [get_attribute Spin max_capacitance]

if {$NEW_CAP > $MAX_CAP} {

set MAXJ3AP $NEW_CAP

}

}

setjoad $MAX _CAP [all_outputs]

约束输入驱动其实就是定义驱动输入的电阻,转移时间,即边沿变化的延迟时间是驱动单元的电阻和被驱动单元的电容的乘积决定。

set_drive 用于约束不是被库中的单元驱动的输入。而set_driving_cell用于约束被库中的cell驱动的输入。

By default, Design Compiler assumes zero drive resistance on input ports,

meaning infinite

drive strength. There are three commands for overriding this unrealistic

assumption:

• set_driving_cell

• set_drive

• set_input_transition

set_drive 很少用了

一般用set_driving_cell , set_load用来约束output port,

set_driving_cell/set_input_transition 用来约束input

port

对于pad输出, load一般是10~30pf (很大了),

对于模块输出 ,load一般是

0.XXX pf

对于input transition,一般比查找表再大些的范围内

此处提一下,如果先后两次对一个端口进行约束,那么最终保存的是最后一次的约束。

库里面对每个单元都有描述,比如该单元的功能,时间,面积等等。除此之外,对于单元的每个引脚还提供有设计规则约束(DRC),这些值由设计工艺决定,只有满足这些条件的单元在运行时才会操作正常,因此在设计中有很高的权重。包括:

fanout_load:输入引脚的扇出负载,这个值跟max_fanout有关。

max_fanout:用于定义输出引脚的值。

max_transition:用于定义输入引脚的最大转换时间;

max_capacitance:用于定义输出引脚的最大电容。

如果需要使对时序 功耗 面积估算更真实,使用DCT(DC-topographical)模式可以有效解决DC对RC估算不精确的问题。但是这样需要文件是:

以上设置完成后,可以用check_timing check_design 等语言查看约束是否完整。

本文说所说的时序和负载预算一般有architecture designer完成,确定好后给模块设计人员进行约束。

在DC-tcl命令中一般调整一个语句中顺序不影响整体语句作用,不管怎样,port或net,clk等命令都是在最后。