使用NCVERILOG仿真mos数字电路

0赞在cadence中,使用mos管和电阻构建了数字电路,但是要对这电路进行功能仿真,仿真的激励也比较复杂,不能使用简单的信号源产生,这个时候,就会考虑使用verilog,编写testbench来进行仿真。

但是电路是由mos管构成的,是不能直接进行verilog仿真的,就需要进行一定的转换。将nmos管和pmos管以及电阻,进行等效的verilog描述。这个时候,就需要使用verilog的开关建模了。

Verilog语法中,有定义几个开关建模的原语。

这里,使用两个就好了。分别是tranif0和rtran。

tranif0(inout1,inout2,control) 当control信号有效的时候,inout1与inout2相连,否则没有驱动源的端口为高阻。

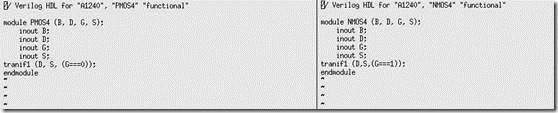

使用该原语对pmos和nmos进行functional描述

左边是nmos,右边是pmos。

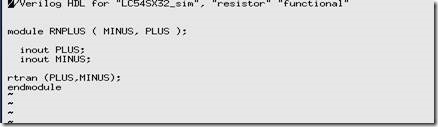

rtran(inout1,inout2),相当于两边是相连的。

对电路图中使用的mos管和电阻进行functional描述后,就可以进行仿真了。

首先是将电路图做成一个symbol,对外引出管脚。

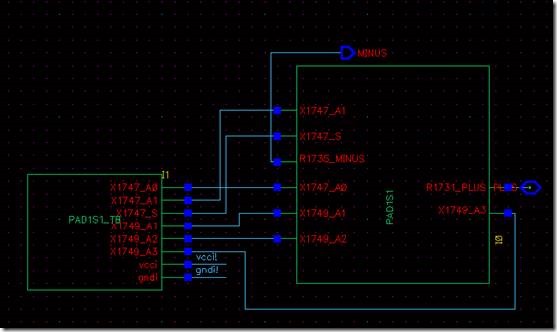

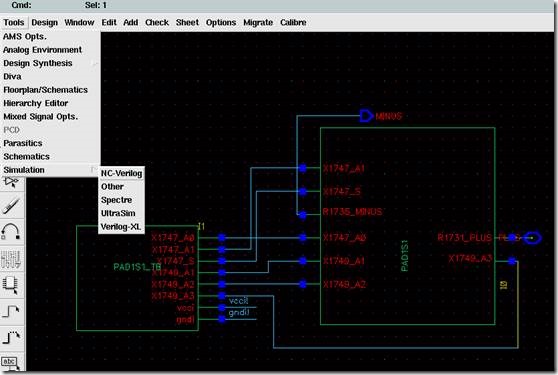

如我要仿真如下数字电路,首先将该电路做成一个symbol。

然后开始编写testbench。编写testbench后,在将该testbench做成一个symbol。

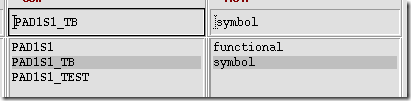

TB便是编写的testbench。有两个view,一个verilog的functional描述,一个是symbol。

最后新建一个原理图,将上述两个symbol调用进来,进行连线。

这样,就完成了电路图的工作,剩下就只要使用NCVERILOG进行仿真即可了。

这里要注意VCC和GND的处理。在电路图中,有VCC和GND,对这两个处理,在TB模块中编写VCC和GND的输出,并使用supply1和supply0这两个语句对VCC和 GND定义。然后在总电路图中,将TB模块的VCC和GND用连线连出,并且给连线命名为仿真电路中的电源和地的连线的名字,这样就将仿真电路中的电源和地设置为1和0了。

接下来就进行仿真。

选择NCVERILOG。启动软件。

依次点击左边的按钮。

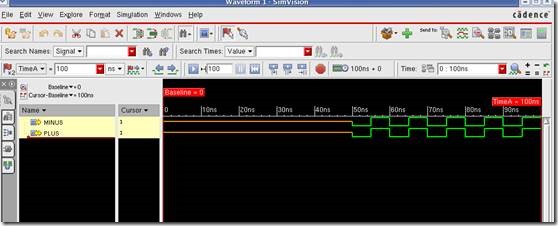

就弹出仿真界面。

将需要的波形添加进波形窗口。

选择仿真的时间,点击播放的箭头即可仿真,得到仿真波形。

这样,就实现了仿真电路图。

其实也比较简单:

编写mos管和电阻的functioal描述,将电路图做成symbol,

编写testbench,并将其做成symbol。

将两个symbol连接起来,直接使用NVCERILOG进行仿真。