sv的数组参数传递

0赞

发表于 4/6/2018 7:11:06 PM

阅读(6140)

systemverilog中,如果一个函数的参数为数组,那么在外部调用这个函数时,可以向这个数组参数,传递一个真正的数组,也可以通过 '{}方式,传递一个常量数组。这样,可以避免在外部定义一个数组,对数组进行赋值,然后进行传递。

格式为以下:

'{数组索引:值, 数组索引: 值, 数组索引: 值 ….}。

数组索引没有顺序要求。

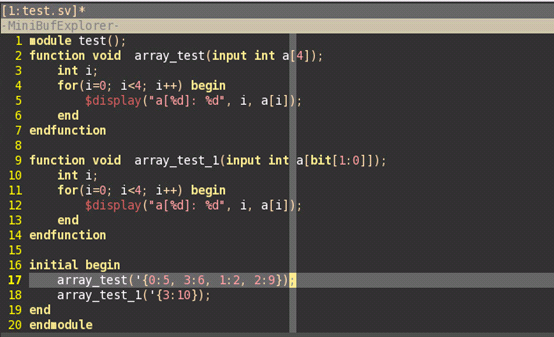

如以下代码进行测试:

定义了2个函数,array_test,输入参数为大小为4的int类型的数组。

array_test_1,输入参数为大小为4的int类型的关联数组。

在initial中,分别调用array_test和array_test_1函数,传入常量数组。

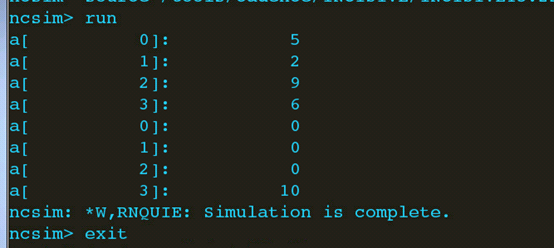

打印结果为:

这里要注意,对于array_test函数,因为参数是大小为4的int类型的数组,所以调用array_test函数时,要传递一个大小为4的int类型的数组。

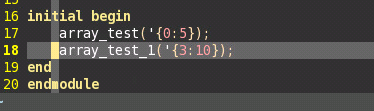

如果,以下面的代码调用:

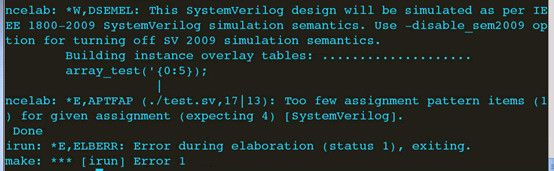

就会出现如下错误,提示,参数不匹配。

对于array_test_1函数,因为输入参数为关联数组,因此在调用array_test_1函数时,可以不用传递整个数组,只传递数组的一部分,其余没有传递的部分,均被当成0处理。所以在打印结果中,数组的第0项,第1项,第2项的值,均为0,只有第3项为10,和传递的参数一致。