ISE VS VIVADO, 哪个坑更深?以FFT为例比较两个软件综合布线后的资源使用情况

0赞作者:刘初一

从10年前接触FPGA开始,一直在用XILINX。记得 最早使用的好像是ISE6.X, 到现在的ISE14.7和VIVADO14.2.

10年来,见证了XILINX一直在努力升级,修复BUG,同时也在加倍努力创造新的BUG。终于,他们发现对ISE的修修补补已经不能满足他们对BUG的追求了,于是隆重推出了VIVADO。 一直不知道VIVADO具体啥意思,也没考证过。倒是在路上经常看到叫VIVARO的面包车,不过这车是通用出的,和XILINX没半毛钱关系。

有那么多介绍VIVADO的文章,都只是介绍VIVADO的优势,基本上都是把XILINX的文档翻译一下,很难有直观的认识。那么VIVADO和ISE比,究竟好不好了?如果好,在哪了?下面我以大家都知道的FFT为例,比较一下两个软件的综合布线后的资源使用情况。

该FFT核配置为: 1024点, 16点复数并行输入输出, 13位输入,18位输出,碟型运算因子18位,选择的比较芯片为XC7K325T-2FFG900, 时钟设为250MHz. 设计全部用VHDL编码,RAM DSP等都通过代码来调用(infer),不使用XILINX的原语(PRIMITIVE)或者CORE GEN的IP CORE.

VIVADO和ISE布线后,都能满足4NS的时序要求。整个运行时间差别也不大 。

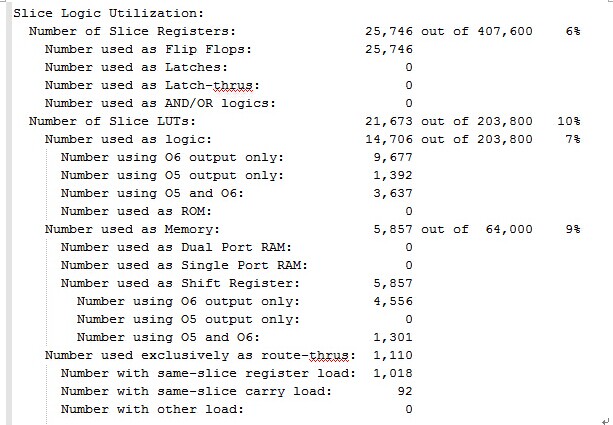

资源使用,无图无真相,直接截ISE的PAR报告

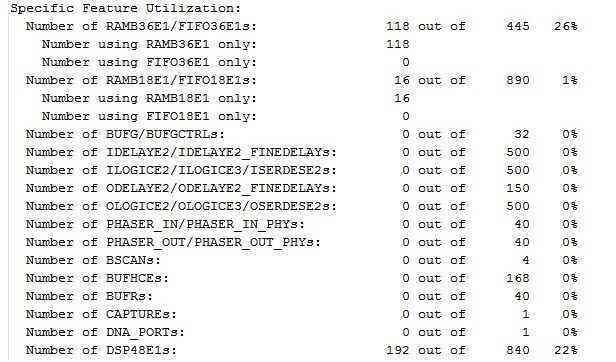

VIVADO的,也是截的utilization报告

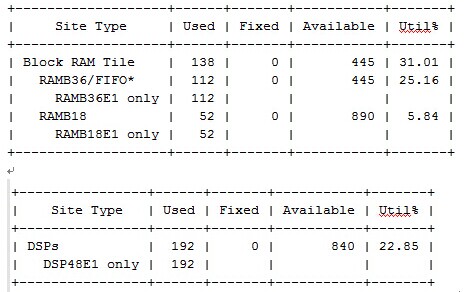

把关键的参数列表比较:

|

|

DFF |

LUT |

RAM18E1 |

DSP |

|

ISE14.7 |

25,746 |

21,673 |

252 |

192 |

|

VIVADO2014.2 |

29,149 |

17,201 |

276 |

192 |

VIVADO使用较少的LUT,但DFF多用了些,不过考虑到在SLICE中一个LUT对应两个DFF,多用些DFF问题不大。在其他的设计中,同样发现VIVADO也同样优化了LUT的使用。

但是VIVADO的RAM却多用了24个,这个问题就严重了。经过对应的比较,发现一些本应该用RAM18E1容量就够的地方,VIVADO却调用了RAM36E1。这方面,VIVADO还要继续改进。由于设计中所有的RAM都是通过代码调用,才会有这样的问题存在。 ISE中也一样有这样的问题。当然如果你使用CORE GEN产生RAM或者使用原语,则不会有这样的问题。总的来说,VIVADO还是有那么一些进步的。由于刚推出不久,还有很多BUG待发掘,待修复,待创造。

对于我个人来说,用VIVADO,完全是被XILINX这货逼的。目前接触的项目还没有用VIRTEX7的,还可以继续用ISE。 不过新做的和以前做的IP,都要用ISE和VIVADO做验证,增加的工作量。另外,VIVADO完全使用TCL,由于不熟悉TCL, 写它的脚本文件,确实花了一些时间,不过写好了,就可以像ISE的BATCH脚本一样,一直用上好多年。

更多“Vivado高效设计案例分享博文”请见:http://comm.ChinaAET.com/xilinx/vivado