Vivado使用——近期小问题、经验总结

0赞

Vivado使用——近期小问题、经验总结

1、Logic Analyzer的使用

《vivado逻辑分析仪的使用》一文中提到如下问题:

打开Hardware Manager,选择Open New Target,按照向导走完,发现无法和ILA建立通信链接。

原因:在选择待抓取信号的时钟域时,Vivado一般默认定位PS_CLK0,所以只有PS运行起来了,该时钟信号有输出,ILA才正常工作。因此在程序未run起来的情况下,会出现无法建立通信的错误。

解决:首先在SDK中完成FPGA Bitstream的download,设置断点,点击Debug按钮,进入main函数(直接run也可以,视需求而定);然后再返回Vivado主界面,打开Hardware Manager,Open New Target,这时,Vivado会自动检测到正在工作的ILA。

2、如何删除整个net网络中的某根连线

在Block Design阶段,将某个IP的pin连接到net网络中时,一旦连接成功,会发现单击刚刚连接的线,会选中整个net网络,那么如何删除net中的某一段连线呢?

如果你很快意识到自己的失误,那么有可能利用“撤销”功能实现该线的删除。但是,如果是保存过的工程,或者是后期检查时发现某根线不需要,该怎么办呢?

方法如下:选中你想删除的线所连接的pin,单击鼠标右键,在弹出的菜单中选择“Disconnect Pin”命令,就会删除连接在该pin上的连线,而不是删除该连线所属的网络,如下图所示。

3、TCL的使用

利用TCL实现工程的快速搭建、移植备份是相当方便的,然而单纯地从编程的角度去实现这些想法,可能就没那么简单,需要对Vivado控制指令,IP核属性等方方面面相当了解才行,其实有一个方法可以偷懒:

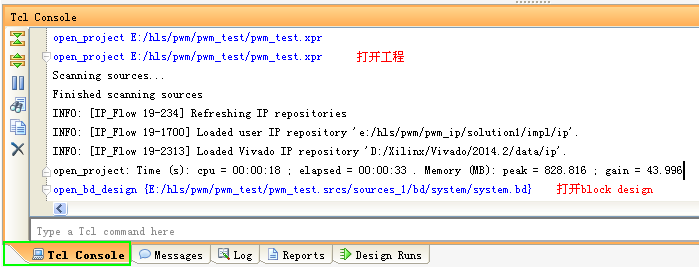

Vivado主界面中有一个Tcl Concole,我们所执行的所有GUI操作,在Tcl Concole中都会有对应的Tcl命令,如下图所示。

借助这一点,我们可以把自己感兴趣的操作、常用的操作对应的指令copy一下,保存起来,这样就可以加速Tcl脚本文件的设计。

4、如何查看IP的Example Desigan

在接触一个新东西,如开发环境、IP核等,Example Design可以帮助我们快速了解它们,从而降低使用难度,缩短开发周期。因此,如何利用Example Design是比较重要的,本小节简要介绍在Vivado下,如何查看IP核的Example Design。

加入到Block Design中的IP是无法查看Example Design的,并不是所有的IP都有Example Design,例如fir、cordic、dds等IP都是没有Example Design的。本文以AXI DMA这个IP为例,介绍如何查看IP核的样例工程。

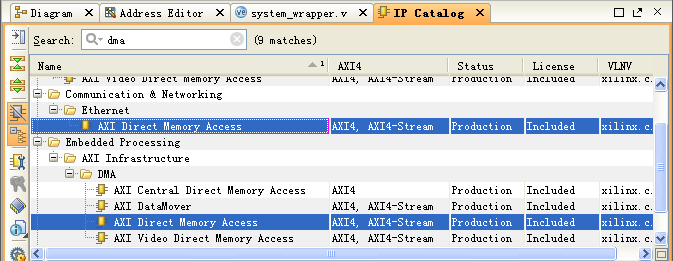

Step1:打开IP Catalog,搜索到AXI DMA这个IP,如下图所示。

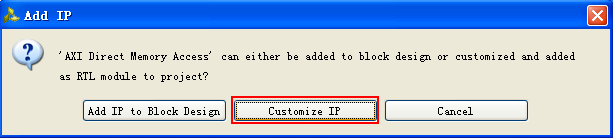

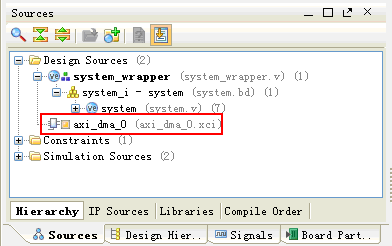

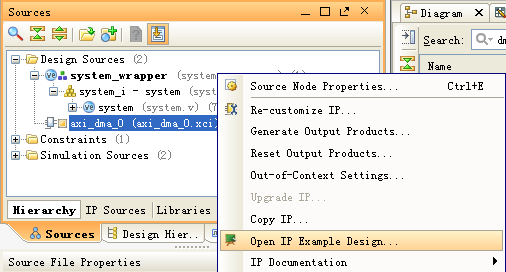

双击AXI Direct Memory Access,弹出下图所示的对话框。 注意,不要选择Add IP to Block Design,点击红色方框内的按钮,弹出下图所示的IP定制对话框。 配置完毕后,选择OK,IP的相关资源会添加到工程的Design Sources文件夹下,如下图所示。 选中axi_dma_0,右击鼠标,在弹出的菜单中选择“Open IP Example Design…”,按照向导打开样例工程即可。

5、未解决问题:

一位网友的问题,在SDK中Debug/Run的时候提示上图所示的错误。他把工程发我了,但是工程在我电脑上跑没问题,我这是XP+Vivado2014.2,他的环境是win 7 + Vivado2014.2

查了一下,不只有一个人碰到这个问题,求高手解答~

版权声明:

本文由博主“cuter”发布。欢迎转载,但不得擅自更改博文内容,也不得用于任何盈利目的。转载时不得删除作者简介和版权声明。如有盗用而不说明出处引起的版权纠纷,由盗用者自负。

博客官方地址:

ChinaAET:http://blog.chinaaet.com/cuter521