【Vivado】如何利用参数控制IP端口的可见性

0赞如何利用参数控制IP端口的可见性

背景见上一篇博文

详细的实现方法:

1、资料准备:

需要被封装的HDL文件(替换为你自己的文件,参照之前的博文进行IP封装),为简单起见,这里只用一个文件,源码如下:

module timing( input iRst_n, input iClk, output oHsync, output oVsync, output oHblank, output oVblank, output oActive_video, output [31:0] oData ); ////////////////////参数,默认为VGA时序///////////////////// parameter SHOW_OR_NOT = 0; // Horizontal Parameter parameter H_RIGHT = 8; // H Right Border parameter H_FRONT = 8; // H Front Porch parameter H_SYNC = 96; // Hor Sync Time parameter H_BACK = 40; // H Back Porch + H Left Border parameter H_LEFT = 8; // H Left Border parameter H_ACT = 640; // Hor Addr Time parameter H_TOTAL = 800; // Vertical Parameter parameter V_BOTTOM = 8; parameter V_FRONT = 2; parameter V_SYNC = 2; parameter V_BACK = 25; parameter V_TOP = 8; parameter V_ACT = 480; parameter V_TOTAL = 525; parameter H_SYNC_START = H_ACT+H_RIGHT+H_FRONT; parameter H_SYNC_END = H_SYNC_START+H_SYNC; parameter H_SIZE = 799; parameter V_SYNC_START = V_ACT+V_BOTTOM+V_FRONT; parameter V_SYNC_END = V_SYNC_START+V_SYNC; parameter V_SIZE = 524; reg [11:0] hcount,vcount; assign oHsync = (hcount>=H_SYNC_START && hcount<H_SYNC_END)? 1'b1 : 1'b0; assign oVsync = (vcount>=V_SYNC_START && vcount<V_SYNC_END)? 1'b1 : 1'b0; assign oHblank = (hcount>=H_ACT)? 1'b1 : 1'b0; assign oVblank = (vcount>=V_ACT)? 1'b1 : 1'b0; assign oActive_video = (~oHblank) & (~oVblank); assign oData = (oActive_video == 1'b1)? 32'h00ff0000:32'h0; //--------------------------------------------- // 计数进程 always @(posedge iClk or negedge iRst_n) begin if(!iRst_n) begin hcount <= 12'b0; vcount <= 12'b0; end else begin if(hcount == H_SIZE) begin hcount <= 12'b0; if(vcount == V_SIZE) vcount <= 12'b0; else vcount <= vcount + 1'b1; end else hcount <= hcount + 1'b1; end end endmodule /*---------------end of file--------------*/

简单说明一下:

这个文件很简单,是VGA的时序,正如注释所说:

////////////////////参数,默认为VGA时序/////////////////////

parameter SHOW_OR_NOT = 0;

SHOW_OR_NOT参数是控制端口显示/隐藏的关键。

2、关键步骤

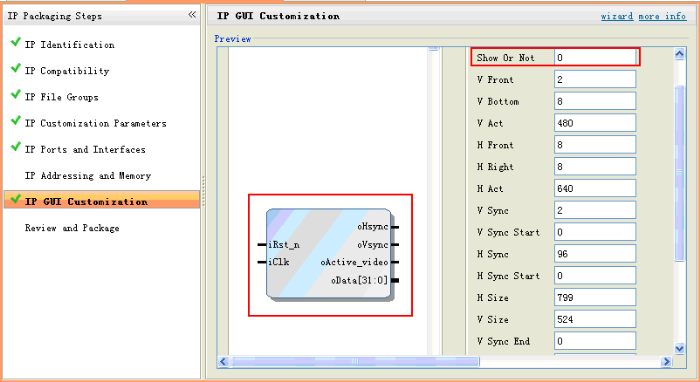

封装IP的方法就不多说了,参照之前的博文吧,按照向导进行完毕后,界面如图1所示:

图1

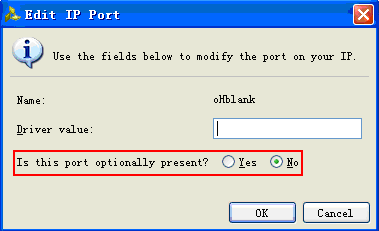

红色方框内文字:“Enablement Dependency”,百度翻译结果是“启用依赖”,好吧,多少能看出来,这个和端口的可见性是有关联的,双击对应端口的Enablement Dependency,弹出图2所示的对话框。

图2 端口编辑对话框

如图2所示红色方框内的提示:该端口是否选择可见?,选择是,对话框界面变化为图3所示。

图3 选则Yes后,界面发生变化

选择Yes之后,图2所示的界面增加了图3红色方框内的内容。

在文本框内输入我们设定好的参数SHOW_OR_NOT,然后点击OK。同样的方法设置端口oVblank,设置完毕后,我们看一下GUI的界面效果,如图4所示。

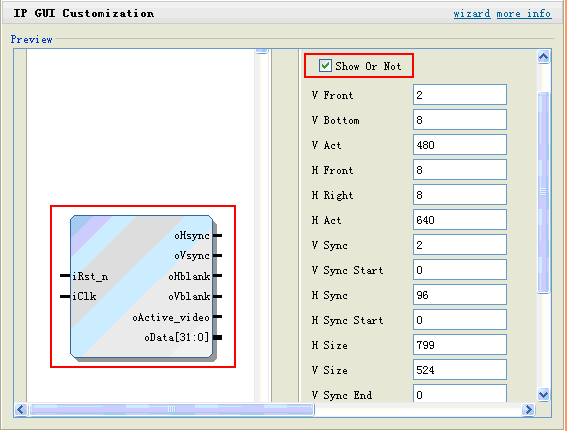

图4 GUI界面

从IP Symbol可以看出,oHbalnk、oVblank被隐藏掉了,这是由于我在写代码的时候给SHOW_OR_NOT定义了一个默认值0。到这里,功能实现还不是很完美,没有定义它的数据类型,端口的可见控制不能及时变化,下面我们更改一下SHOW_OR_NOT的属性,将他变为鼠标可勾选/取消的选项,端口也同时发生变化。

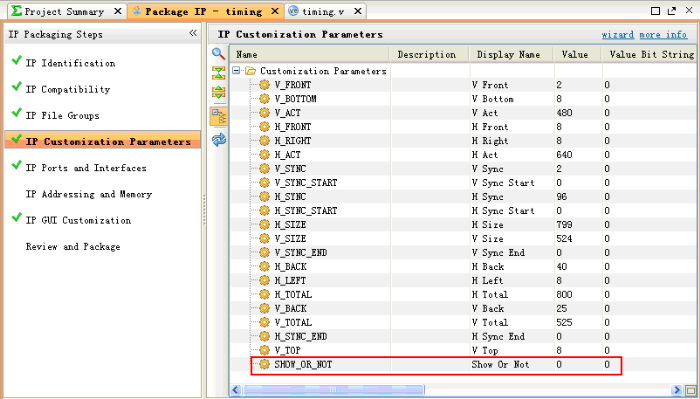

选择IP Customization Parameters,可以查看到所有参数,如图5所示。

图5 查看参数

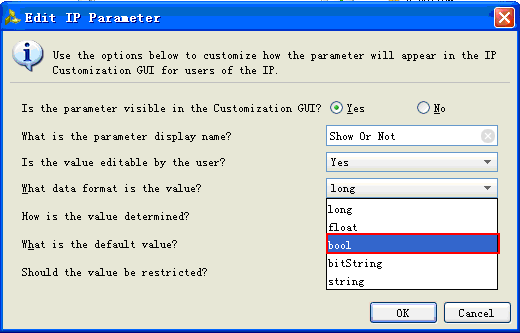

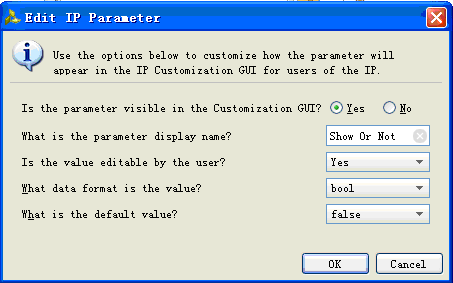

选中SHOW_OR_NOT参数,右键选择Edit IP Parameter,弹出图6所示的对话框。

图6 编辑SHOW_OR_NOT属性

选择数据类型为bool,default value随意,我选的是false,结合上面的端口设置,意思就是端口默认不可见。编辑完毕的SHOW_OR_NOT属性如图7所示。

图7 SHOW_OR_NOT属性

然后查看一下Symbol的效果,如图8所示。

图8 Symbol效果图演示之端口可见

图9 Symbol效果图演示之端口隐藏

实际测试:

以上都是在IP打包工程中的效果,下面我们建立工程实际测试一下:

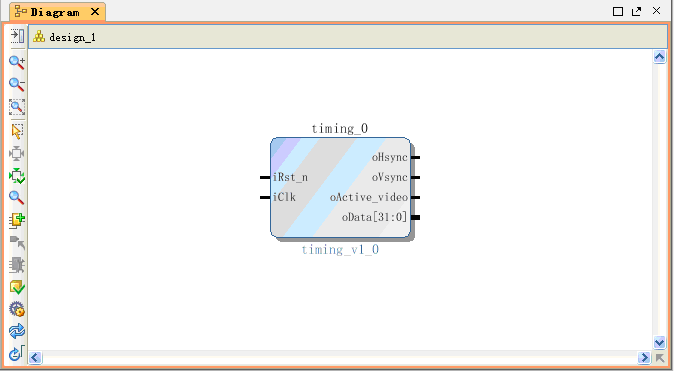

建立一个新的Block Design,将我们做好的timing IP加入到BD中,效果图如图10所示:

图10

双击timing_0,设置参数,如图11所示。

图11 勾选SHOW_OR_NOT

设置完毕后点击OK按钮,返回BD界面,timing的symbol发生变化,效果如图12所示。

图12 显示隐藏端口效果图

3、搞定,收工!

版权声明:

本文由博主“cuter”发布。欢迎转载,但不得擅自更改博文内容,也不得用于任何盈利目的。转载时不得删除作者简介和版权声明。如有盗用而不说明出处引起的版权纠纷,由盗用者自负。

博客官方地址:

ChinaAET:http://blog.chinaaet.com/cuter521