vivado设计一:建立第一个入门工程(基于zybo)

0赞软件:vivado 2013.4

电脑:xp系统

硬件:zybo(基于xilinx 的zynq-7010主控芯片)

实验一:利用vivado建立一个嵌入式系统(之前用PlanAhead在zed实现过,现在换成vivado和zybo了,感受一下不同的地方)

启动vivado,建立新工程

选择next,填写工程名称和选择工程路径

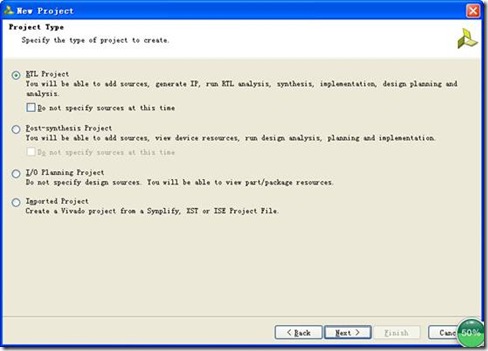

Next,RTL工程走起:

Next,选择为verilog

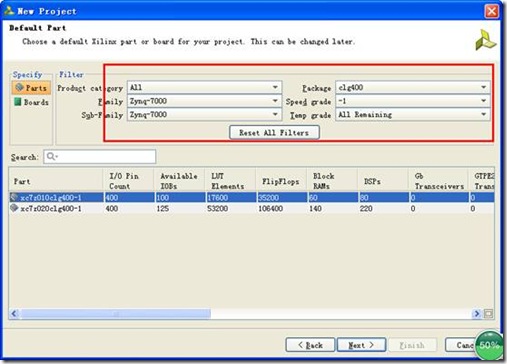

连续三次Next,选择平台,这里我们使用的是zybo了:

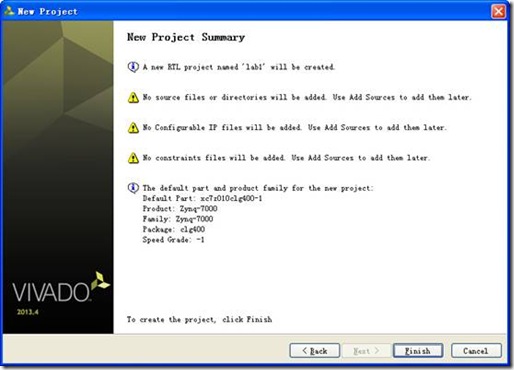

Next,然后finish,就建立了一个空的vivado工程

来到工程主界面:

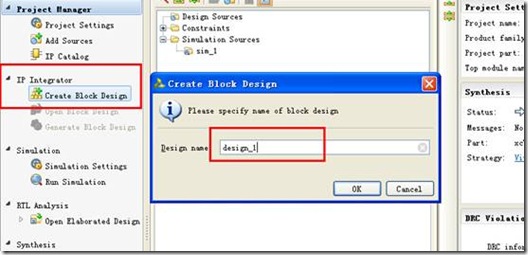

Create Block Design

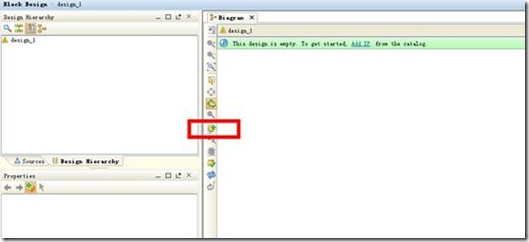

点击ok,Add IP

搜索z,选择红色的zynq7 Processing System

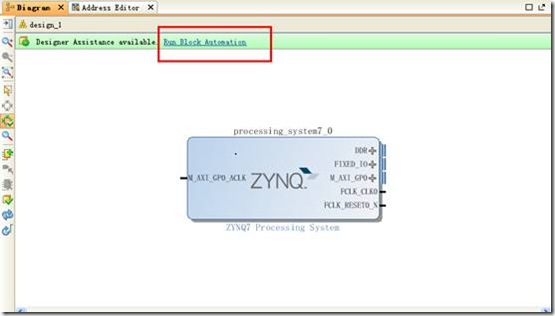

双击zynq7 Processing System,点击Run Block Automation

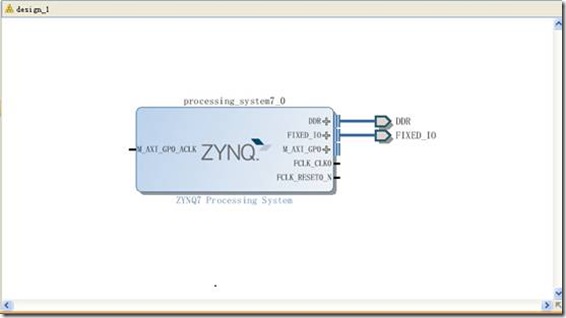

出现了:

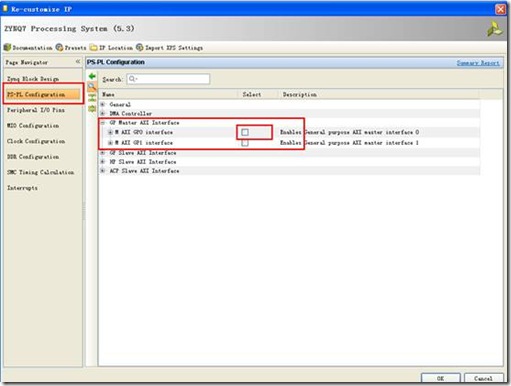

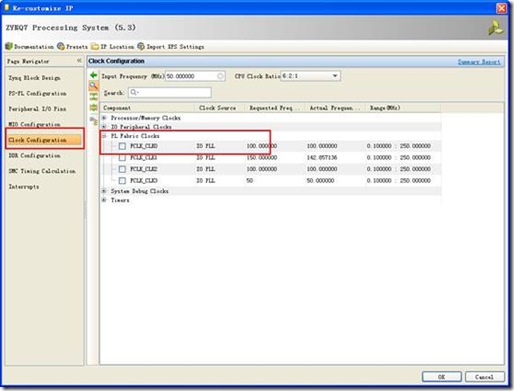

双击上面出现的图:添加配置文件:

点击ok,回到界面,继续zynq7 Processing System

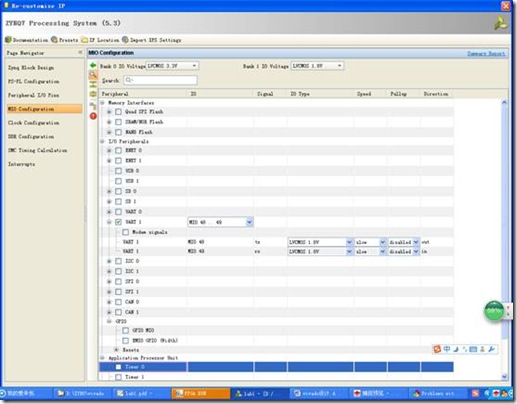

注意下面的非常重要只留下uart1:

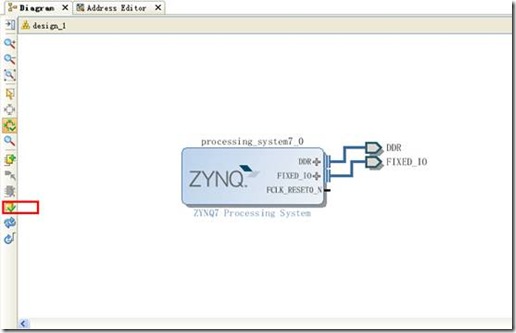

点击ok,回到主界面:

点击上述的validate design ,没有错误

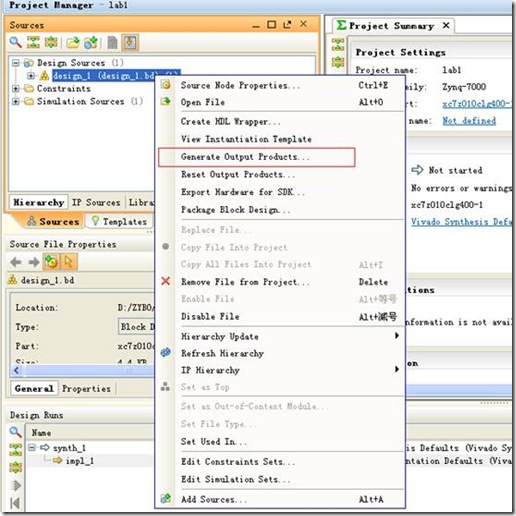

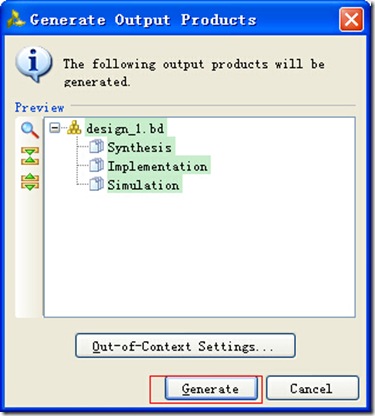

Generate

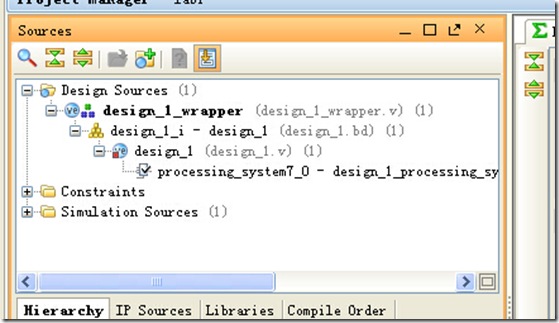

File->Export > Export hardware for SDK

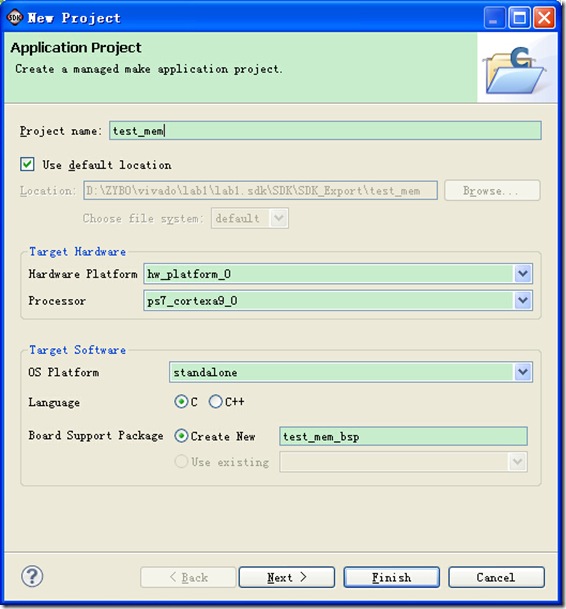

建立应用程序工程

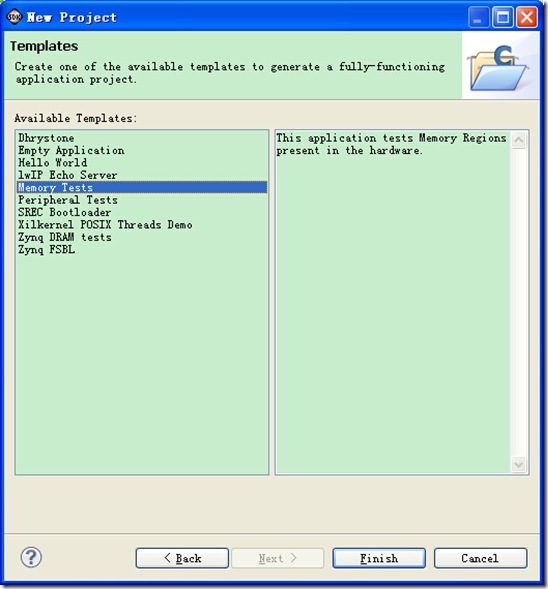

选择模板:

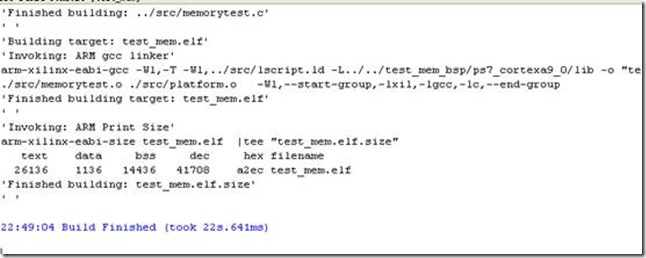

产生模板后,打开memorytest.c,在空白处按下个Enter,保存,这个时候就会重新编译,生成我们需要的elf文件:

好,在zybo上设置为JTAG启动,接好uart线,选择usb供电

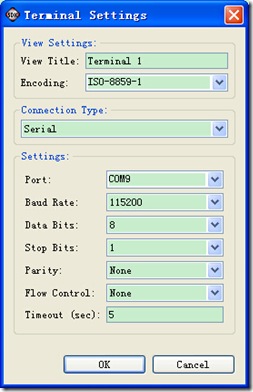

下载elf文件,可以看到信息如下:

zedboard--ps工程helloworld的建立

http://blog.chinaaet.com/detail/34607

vivado设计一:建立第一个入门工程(基于zybo)

http://blog.chinaaet.com/detail/35736

第一个是从ISE的PlanAhead从开始建立一个zynq的纯ps的工程

第二个是从vivado中直接建立的一个PS工程,这里都没有用到PL。

基本流程是差不多的,还无法体会vivado的强大之处,有待继续学习和发掘。