【设计心得】modelsim三种仿真实验结果对比

0赞既然决定认认真真搞FPGA,学好modelsim,那么就一路坚持下去!首先,继续摸熟modelsim仿真。

今天摸清了用Modelsim做功能仿真,综合后仿真,时序仿真。纪录下过程和对比下结果。

首先在前面的博客中,各种环境已经在前面搭建完毕,包括编译仿真库等,一会会有一个简单的各个仿真比较例子。

FPGA各种仿真概念(摘自CB书中)

1. 功能仿真(前仿真),验证逻辑功能,不用全编译,即ctrl+k就可以了。验证电路功能是否符合设计要求。这个仿真一般是必须做的。

2. 综合后的仿真,这个是FPGA综合产生的网表(会有门延时),一般是不用做的,这里要对比几个仿真结果的不同,也做一遍。

3. 时序仿真,布局布线后的仿真,这个时候就包括了布线的延时,一般这个也需要做的。

偶然找到一张笔试卷子的题目的module,就以他为例来做了:

首先写好v文件:如下:

/*-----------------------------------------------------------------------

Author : xzy610030

Technology blogs : http://blog.chinaaet.com/xzy610030

Email Address : xzyfeixiang@163.com

Filename : test_for_szaotuo.v

Data : 2014-11-18

Version : 1.0

Description : test there modelsim project

Additional Comments : The entire notice above must be reproduced on all authorized copies.

Modification History :

Data By Version Change Description

=========================================================================

14/11/18 xzy610030 1.0 Original

-------------------------------------------------------------------------

-----------------------------------------------------------------------*/

`timescale 1ns/1ns

module test_for_szaotuo

(

//global clock

input clk, //clk 50Mhz

input rst_n, //global rst_n

//control input signal

input wr_en,

//user interface

output [3:0] wr_cnt

);

//produce the cnt

reg [3:0]cnt;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt<=0;

else if(wr_en)

cnt<=cnt+1'b1;

end

assign wr_cnt={cnt[1:0],cnt[3:2]};

endmodule

写好testbench文件:

/*-----------------------------------------------------------------------

Author : xzy610030

Technology blogs : http://blog.chinaaet.com/xzy610030

Email Address : xzyfeixiang@163.com

Filename : test_for_szaotuo_TB.v

Data : 2014-11-18

Version : 1.0

Description : test three modelsim project

Additional Comments : The entire notice above must be reproduced on all authorized copies.

Modification History :

Data By Version Change Description

=========================================================================

14/11/18 xzy610030 1.0 Original

-------------------------------------------------------------------------

-----------------------------------------------------------------------*/

`timescale 1ns/1ns

module test_for_szaotuo_TB;

//------------------------------------------

//clock generate module

reg clk;

reg rst_n;

reg wr_en;

localparam PERIOD = 20; //50MHz

initial

begin

clk = 0;

forever #(PERIOD/2)

clk = ~clk;

end

task task_reset;

begin

rst_n = 0;

repeat(2) @(negedge clk);

rst_n = 1;

end

endtask

//----------------------------------------------

//the target component instantiation

wire [3:0] wr_cnt;

test_for_szaotuo u1

(

//globol clock

.clk (clk),

.rst_n (rst_n),

.wr_en(wr_en),

//led interface

.wr_cnt (wr_cnt)

);

//---------------------------------------

//system initialization

task task_sysinit;

begin

end

endtask

//----------------------------------------

//testbench of the RTL

initial

begin

task_sysinit;

task_reset;

wr_en=0;

#70 wr_en=1;

#140 wr_en=0;

end

endmodule

那么开始了

一:功能仿真

1.quartus建立工程后,编写v文件,ctrl+k,无错误(当然注意风格)

2.编写testbench文件

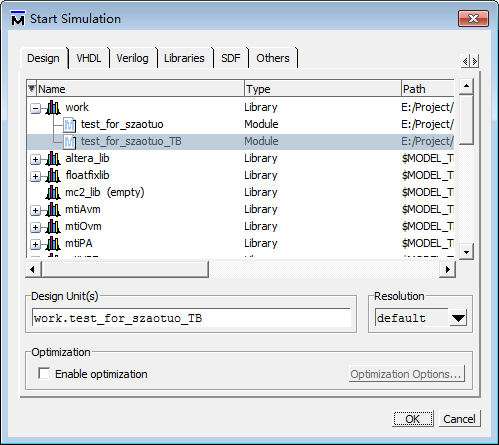

3.建立sim1仿真工程,在sim有单独的sim1的文件目录,将v和testbench拷贝到sim1

这里我们没有用到altera的IP核,所以在library那里可以不用设置路径,如果有用到的话,就要指定路径了。

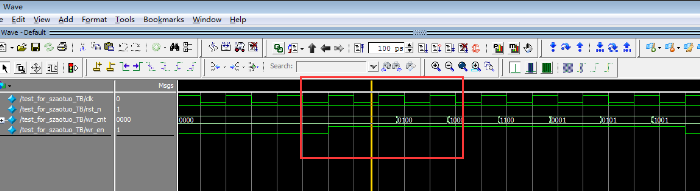

4.仿真,这个前面没什么区别,注意去掉 Enable optimization

5.添加信号,run 500ns

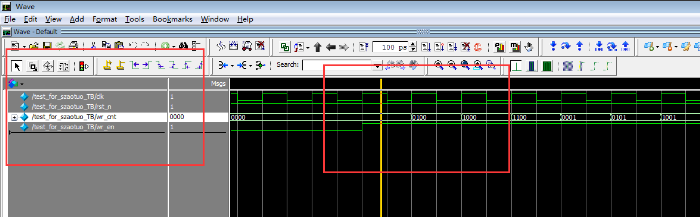

可以看到,在wr_en拉高的时候,cnt立马就有输出,这是没有任何延时的,是纯粹的功能仿真。功能仿真需要文件:v源文件+testbench+指定仿真模型(altera仿真库等,等下就有用到)

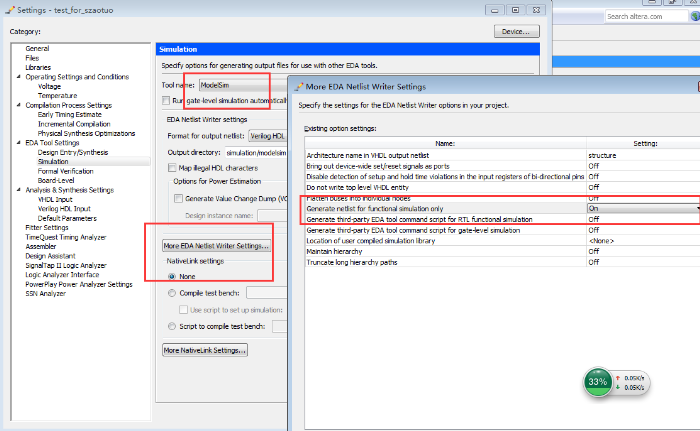

二:综合后的仿真

1.关闭modelsim的sim1工程了,建立sim2文件目录,回到quartus

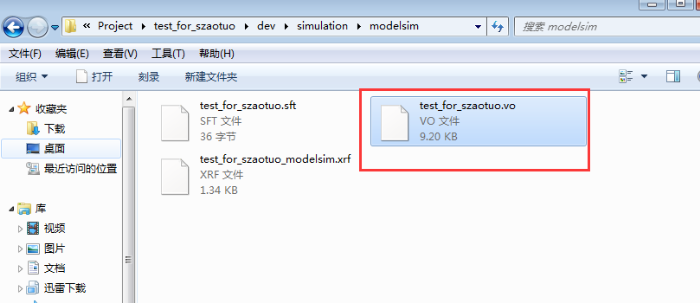

2.然后,点击编译,会在dev目录下产生一个simulation文件夹,找到vo文件

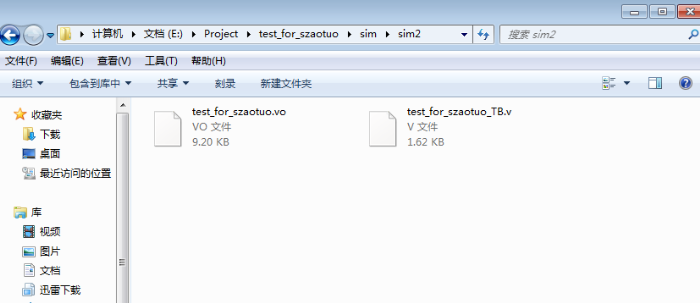

3.建立sim2的modelsim的工程,和上面的类似,但是注意:将vo文件和testbench文件拷贝到sim2文件夹,这一点和上面不同哦。

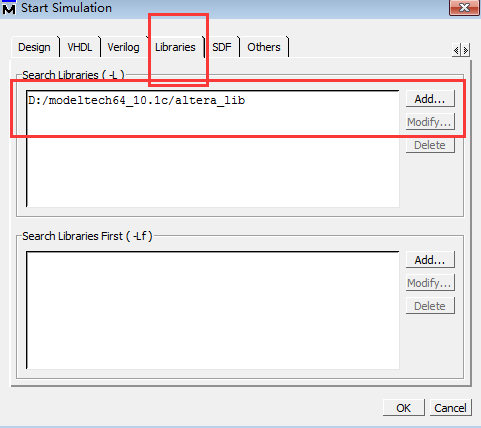

4.然后和之前不同的是,我们需要添加altera的仿真库,因为不同的器件的门延时不同,网表和器件有关。

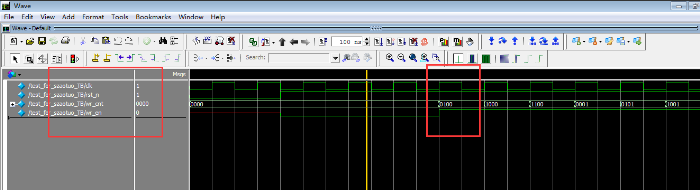

5.然后添加信号,仿真,run 500ns

虽然,clk和wr_en是同时上升沿,但是cnt的输出晚了一个时钟周期。

综合后的仿真:vo(verilog网表)+testbench+仿真库模型

接下来看看时序仿真是怎么样子的

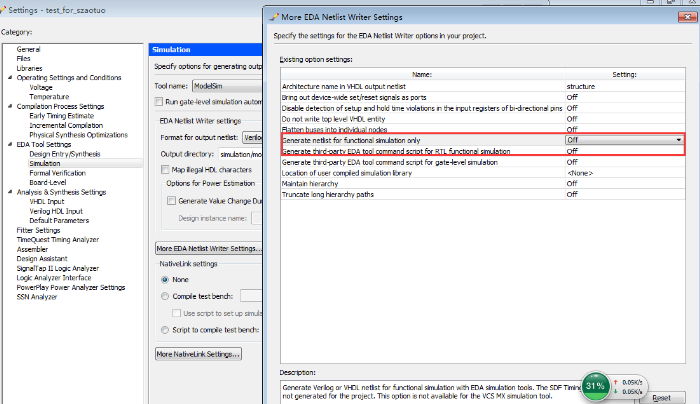

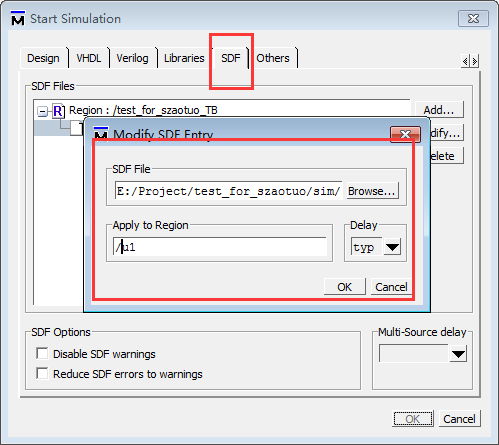

三:时序仿真:注意我这里没有添加约束,即这个仿真时在没有时序约束下的布局布线的仿真

1.关闭仿真工程sim2,回到quartus,做出一个设置

2.在综合后的仿真,我们有一个设置为on,现在我们改为off,这样,除了生成网表vo文件,还会生成布局布线后的延时文件sdo文件

3.建立sim3文件目录,将vo和sdo和testbench拷贝到sim3,建立sim3的modelsim工程

和综合仿真多了一个地方,就是sdf那里添加sdo文件,apply to Region那里是testbench的例化的文件,我例化为u1

综合仿真时1个clk的延时,这里不只一个clk延时,可以清楚的看到3个仿真的结果。

时序仿真:vo网表+testbench+仿真库+sdo延时文件

总结:

学会了综合后的仿真:需要哪些文件,以及一般流程。

学会了时序仿真:需要哪些文件,以及一般流程

在即使有用altera IP 核的仿真,只要在仿真的时候,设置好那个library的搜索路径就可以了,因为我之前已经编译了,在启动的时候,那些就是资源库了,设置好路径就可以了。