EDK之路(3)——自定义IP(XPS部分)

1赞工程目的

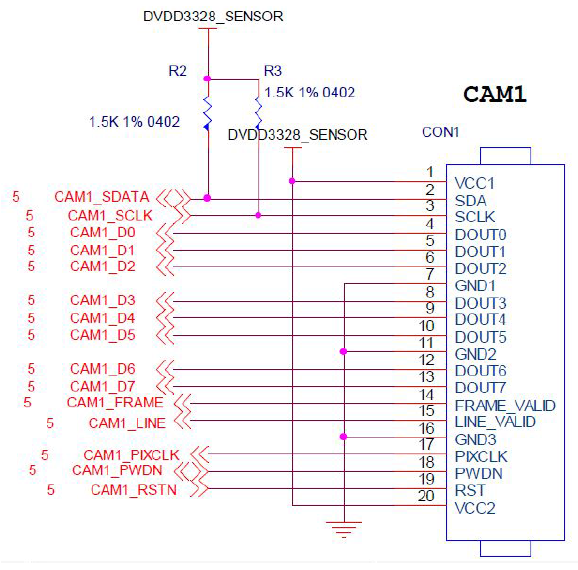

本工程目的是自定义一个IP,用于对OV2643摄像头的进行配置。重点有3个:

(1) 需要在定制板上建立系统(即我们使用的不是现有的开发板,无官方的板级支持包);

(2) 自定义IP;

(3) IIC总线在EDK中的使用。

通过该例程,熟悉自定义IP的建立与使用(在实际应用中,很多都是需要自建IP),以及了解在EDK中实现一些特殊协议的方法(这里是IIC)。(注:将省略部分步骤)

建立最小系统

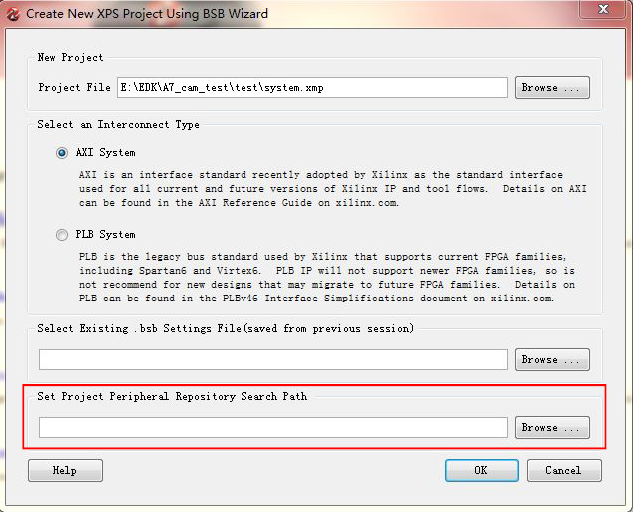

在建立系统时,由于我们使用的是自己制作的板子,不存在板级支持包(bsp),因此在下图中的红框处保留空白,无需添加库文件。

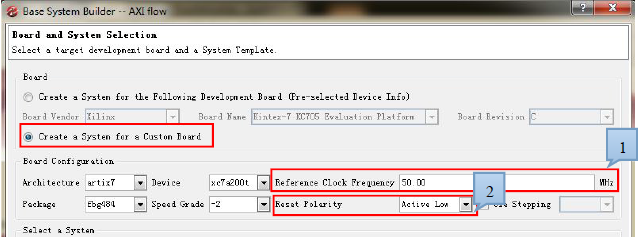

选择Creat a System for a Custom Board。如图配置符合我们板子的信息。1处表明的是外部晶振的频率,其大小并不一定要大于后面所提到的处理器的频率的,如果处理器频率比外部晶振频率高,系统会自己倍频实现。所设置的外部晶振频率可以在ucf文件中查看。2处表示复位电位,我们的板子是低电平复位,因此这里选择Active Low.。这些参数都可以在后面的步骤中查看以及修改。

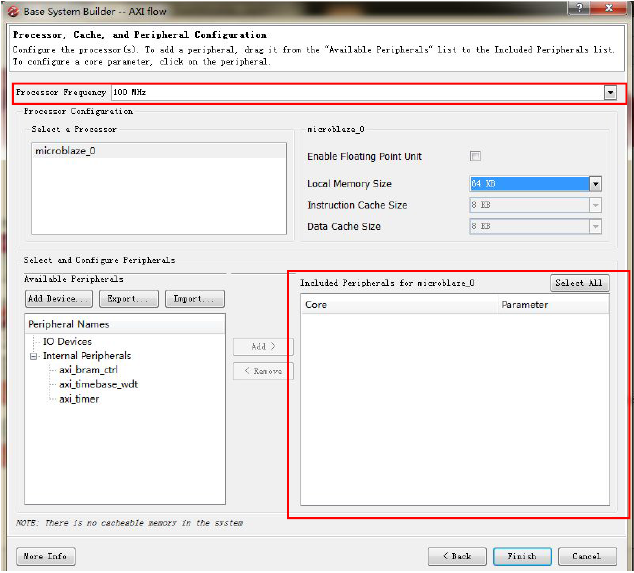

接下来这一步和以前使用开发板时差不多,需要注意的是这里的Processor Frequency是处理器频率。且可以看到下面外设框中是空白的,这是因为我们是自制板,不带有BSP库文件。点击Finish.

添加IP

添加AXI_IIC

在IP Catalog中直接搜索IIC即可出现AXI IIC Interface的IP核。

连接好端口即可,该IP核在硬件连接上没什么好说的,重点是软件方面的应用,这个后面再说。(这里还连接了chipscope的端口,为了更好的查看信号,至于chipscope的使用,这里暂时忽略,将在以后的文章中详细描述chipscope的使用)。

添加自定义IP核

点击Hardware->Create or Import Peripheral

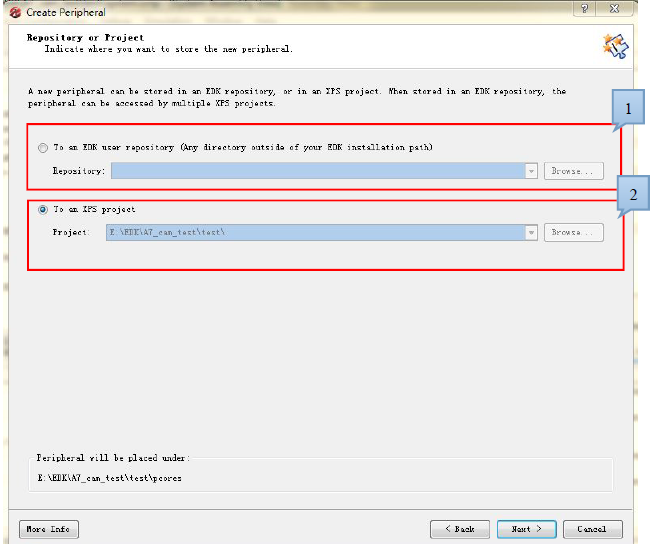

之后几步比较简单,略去。到达这一步时,1表示将该IP核创建到库中,这样方面以后我们对它的多次利用;2则表示创建到当前工程中,这里我选择的是2。

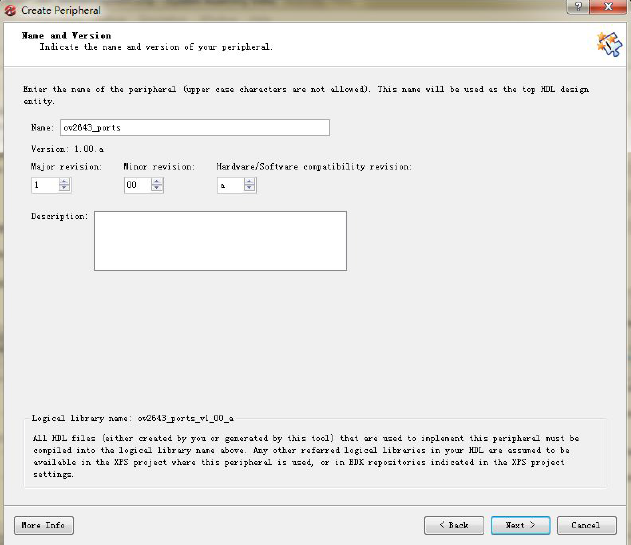

将该IP核命名为ov2643_ports,关于命名也存在规则,不能有大写字母,不能以数字开头,如果命名有误,字体颜色为红色。下面的1.00.a为其版本号。

到达这步后,需要勾选User logic software register。这样才能通过操作寄存器来实现我们的功能,才符合EDK中利用软件,而不是纯硬件的思想。

在这选择寄存器的数量,一个寄存器有32位,每一位可表示一个端口,也就是说一个寄存器便可以满足32个端口的使用。但为了后面更好的理解verilog程序,这里设置两个寄存器,输入使用一个寄存器,输出使用另一个寄存器。

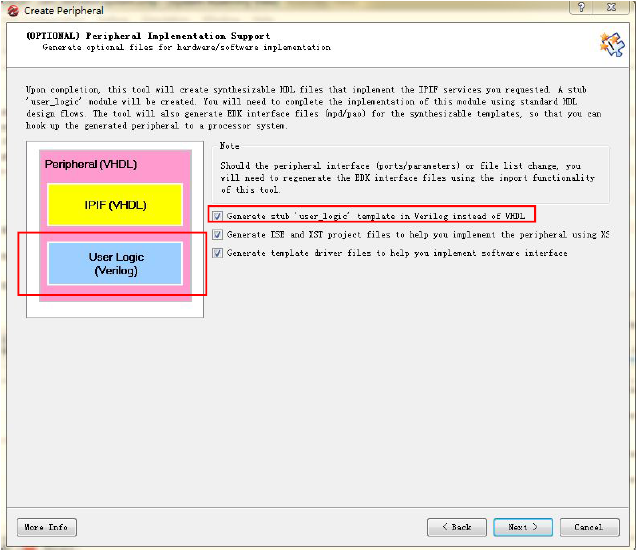

在这步中,三个都勾选上。注意对于第一个,因为我更擅长verilog,所以勾选这个,这样在该IP核的User Logic部分即采用的是verilog,更喜欢VHDL的人可不勾选此项。

接下来需要修改各种文件,为自定义IP添加端口信息。

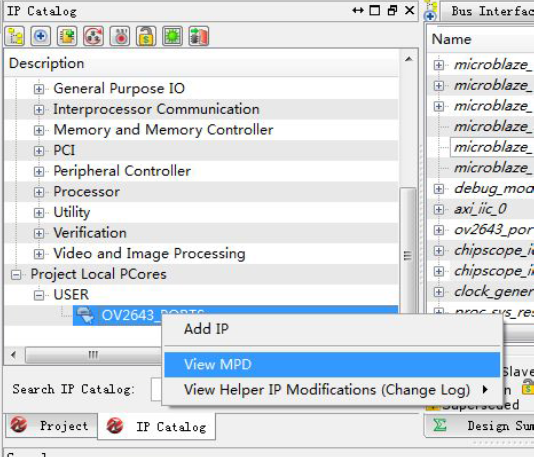

首先是MPD文件,在Project Local PCores->USER中找到刚刚建立的IP核,右键点击View MPD,即可打开MPD文件。

在#PORT部分添加端口如下:

接下来是VHDL文件和verilog文件。这两个文件在工程文件夹->pcores->ov2643_ports_v1_00_a->hdl中。打开两个文件,按照里面所提示的位置以及对应的格式修改即可。

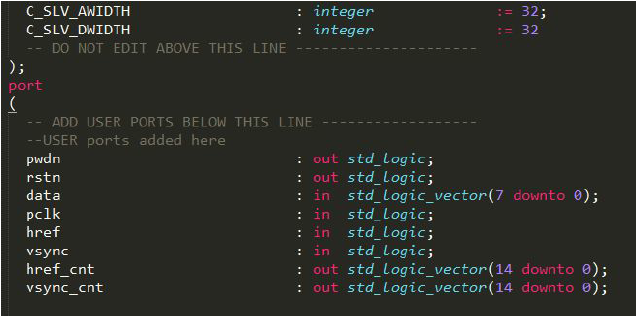

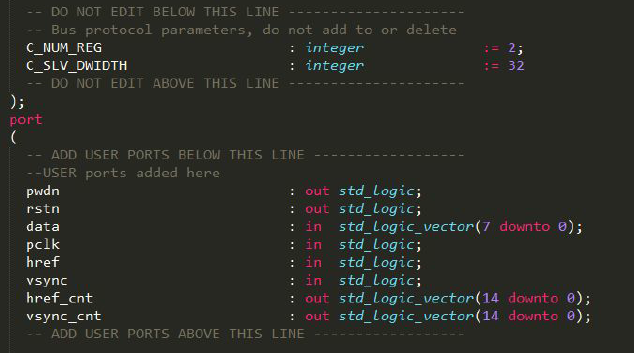

VHDL文件修改,有3个地方需要添加:

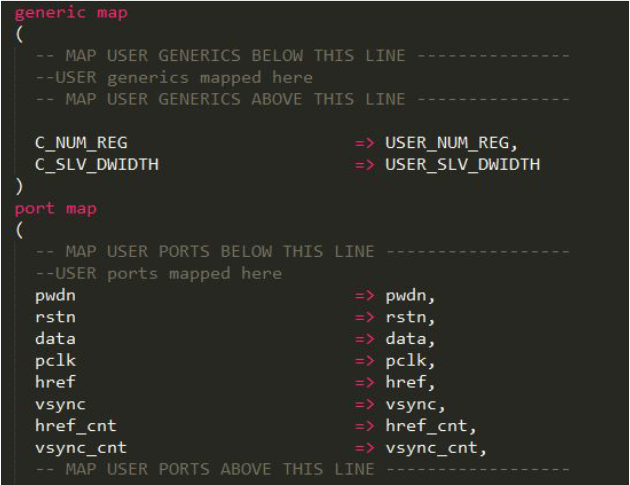

verilog文件修改,首先添加端口:

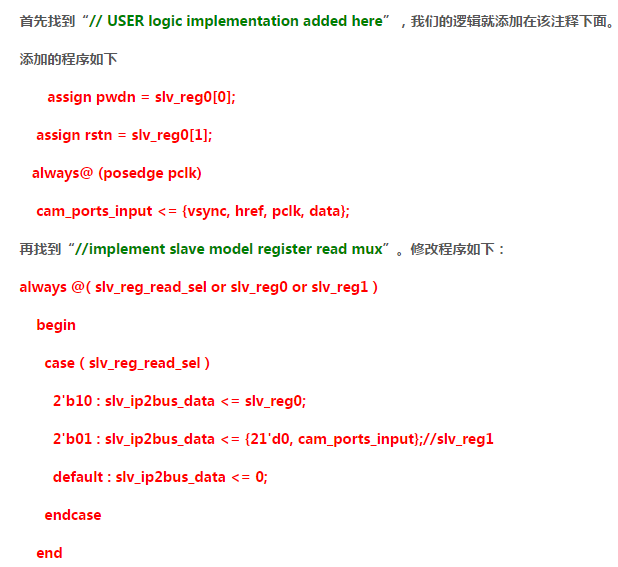

接着重点介绍一下如何增加自己的所需的逻辑。

这两段的意思很简单,就是slv_reg0作为输出寄存器,slv_reg1作为输入寄存器(我们也可以把所有端口都放在一个寄存器里面)。我们可以通过操作这两个寄存器来获取数据,输出数据等。

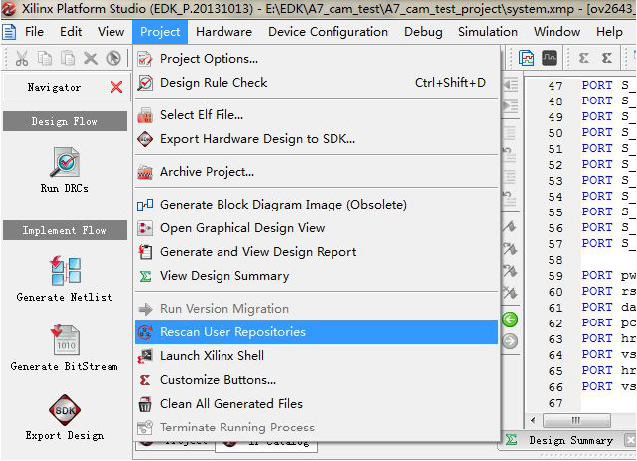

修改完毕后,一定要点击Project->Rescan User Repositories,修改才能生效。

接下来和自带IP核的操作就是一样了——添加IP核->连接端口->修改ucf文件即可。

限于篇幅,SDK部分将在下篇——《EDK之路(3)——自定义IP(SDK部分)》中说明