基于AXI总线的DDR仿真模型

2赞

发表于 2017/7/5 下午5:42:04

阅读(5562)

在xilinx平台下,经常要进行基于AXI总线的IP开发。尤其是当要使用DDR时,仿真就存在很大的问题了。之前我们的解决办法是修改接口,然后连接到一个模拟DDR的寄存器组中。但这样做一方面频繁修改接口,相当麻烦;另一方面仿真行为与下板行为不完全一样,不方便找出bug。所以我就决定建立一个DDR AXI 仿真模型来用于AXI总线下的仿真。其思想和原来的方法一样,都是在testbench中建立一个寄存器组来模拟DDR。只不过不修改接口,而是直接用AXI总线的接口来进行行为模拟。

首先,我们先来了解下AXI总线的主要接口与行为:

AXI总线信号说明:

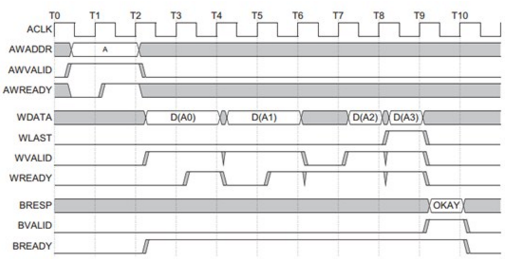

写数据信号图

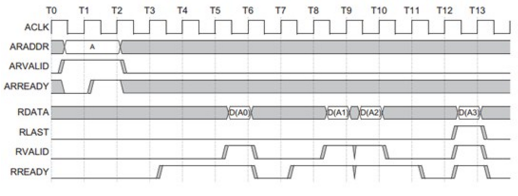

读数据信号图

在了解了AXI总线的接口与行为后,下面我将对我的代码做出解释(代码文件见附件):

1,本demo设计了3个写通道,3个读通道。可根据需要按类似模式修改相关参数和状态机

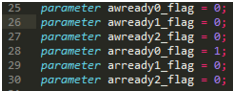

2,由于ddr反馈的ready信号可能是高有效,也可能是低有效。根据实际情况,若是高有效,则相应flag置1,否则置0;

3,设置一个寄存器组,起到DDR作用。在testbench中,寄存器组大小不受限制

4,对ddr_mem进行初始化,瞬间完成。

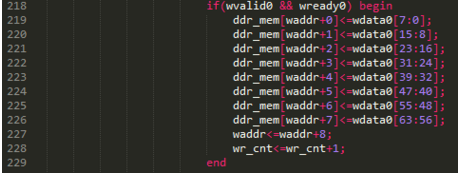

5,这也是需要根据实际情况修改的地方。根据写入宽度,按类似形式增减。下图显示的是每次写入64位。

然后就可以愉快的仿真测试啦!