高级FPGA设计——第二章:面积结构设计

0赞在上一章中,我们提到速度是FPGA设计中的重要特性,现在要说说另一重要特性:面积。

面积过大意味着成本的提升,对FPGA以及ASIC都是如此。因此,我们需要竭力控制面积,可采用以下方法:

1,折叠流水线

在上一章中提到,提高速度的方法之一就是采用流水线结构。但是流水线结构却会增大面积,因为这需要更多的资源保存中间数值,并且某些结构需要复制多个以并行执行。

以乘法器为例:

乘法器本身就是一个具有流水线结构的逻辑链,因此即便对于乘法这种复杂运算,它也能够快速计算出结果。与此同时,乘法器也是一个占用面积特别大的结构,在设计中应慎用。

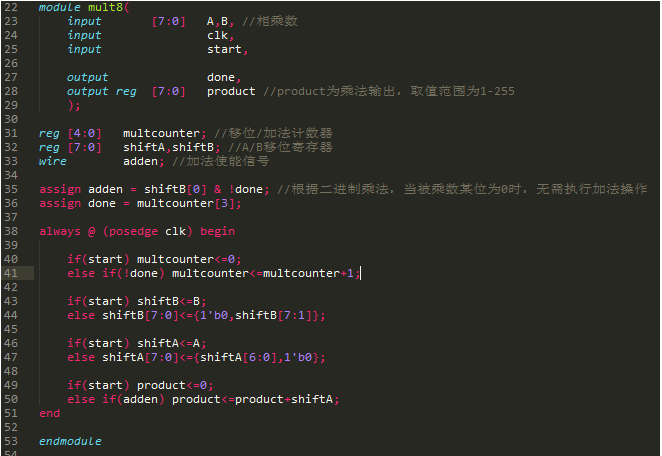

既然不直接使用乘法器,我们可以利用移位和加操作来实现一个乘法操作,如下:

该方案用少量寄存器和一个加法器完成了乘法器功能,减小了逻辑面积。但同时可以看到,该乘法逻辑需要8个时钟才输出结果,即减小面积的同时也牺牲了速度。

2,资源共享

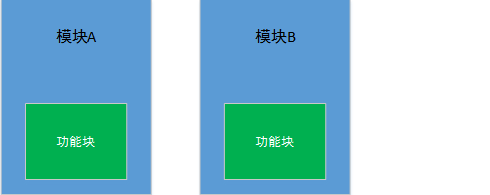

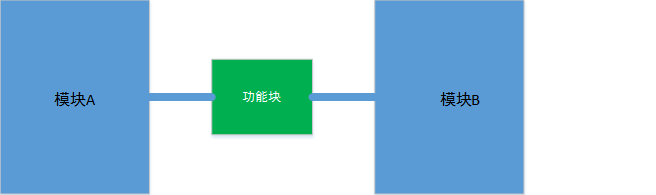

当多个模块都需要使用某一功能块,且不同时使用时,我们有2种方法:

(1) 在每个模块当中都添加一个功能块

(2) 将功能块放置在模块A/B外,模块A/B共同使用该模块

显然,方法(2)能够节约面积。

下面,用一个实例来说明。假设功能块是一个计数器,模块A需要利用计数器每256个时钟标记一个操作。模块B则需要利用计数器每512个时钟标记一个操作。虽然模块A和模块B对计数器的需求不完全一样,但是还是可以采用资源共享的方法。

设置(2)中功能块为一个9位的计数器,计数值即0-511。则该计数器既可以为模块B计数,其低8位同时也可以为模块A计数。

需要注意的是,该方法需满足:

(1) 模块A/B对计数器的起始时间要求时一样的

(2) 模块A/B的计数值呈倍数关系

3,复位对面积的影响

初学FPGA时,我被告知在设计中尽量添加复位端,因为这样可以避免很多未知态的产生,使系统更安全稳定。但是学的深入点后,才知道不必要的复位端可能会导致面积的增加。

(1) 无复位的资源

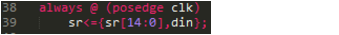

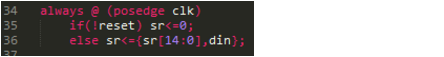

实现1:无复位

实现2:同步复位

实现1与实现2都在实现一个16位的移位寄存器,区别在于实现1无复位,实现2有复位。在xilinx器件中,存在16位的移位寄存器资源SRL16。

当采用实现1代码时,综合工具将自动调用SRL16。

但是采用实现2代码时,由于SRL16并没有定义复位,综合工具将不调用SRL16,而是利用一堆逻辑资源来搭建所需的移位寄存器,造成面积的增大。

同时,即便内置功能模块有复位模块,也需要考虑是同步复位还是异步复位。比如DSP模块就只有同步复位功能,若此时采用异步复位,也将增加面积。

同理,复位RAM是欠佳的行为,特别是当复位还是异步的。

(2) 无置位资源

同(1)理,有些资源无复位功能,有些资源无置位功能,比如8*8乘法器。

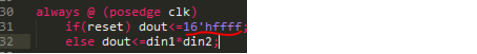

如下代码,若把16‘hffffh改为16’h0000将大大减小面积。因为8*8乘法器有复位功能但无置位功能。

(3) 利用置位/复位触发器引脚

实现1:

实现2:

实现2与实现1的区别在于,实现2利用置位端实现逻辑,从而去除或门,减小面积。同理,也可以利用复位端来去除与门。

综上,要减少面积,就应该充分利用内置功能模块的资源,不附加多余逻辑。具体来说,就应尽可能避免利用置位和复位。