PCIe扫盲——物理层电气部分基础(二)之De-emphasis

0赞连载目录篇:http://blog.chinaaet.com/justlxy/p/5100053481

这一篇文章中,我们主要来聊一聊PCIe中的信号补偿技术(Signal Compensation)——De-emphasis。需要注意的是,Gen1&Gen2与Gen3的De-emphasis实现机制差别较大,而本文只介绍Gen1&Gen2相关内容。如需了解Gen3的相关内容,可自行查阅Gen3的PCIe Spec。

高速信号传输中有一个非常棘手的问题,就是当传输速率变得越来越高的同时,数据间隔单元(Unit Inerval,UI)也会变得越来越小。这导致前一个bit的数据会对后面bit的数据造成影响,如果不去除这些影响,将会导致误码率飙升,甚至通信无法继续。

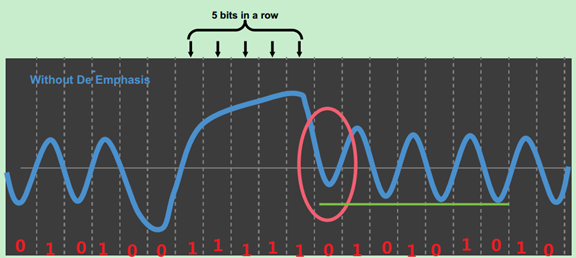

此时,还存在另一个问题,如果系统中出现几个连续的1(或者0),而接下来的信号为0(或者1)时,信号的电压可能达不到要求,如下图所示。这种前面的信号会影响后面的现象,我们称之为ISI(Inter-Symbol Interference)。产生这种现象的罪魁祸首是传输线的介质损耗,具体会在SerDes的专栏文章中详细介绍。

注:虽然PCIe采用了8b/10b编码,但是仍然会出现连续的5个0或者5个1(一些控制字符,如COM)。

为了解决这个问题,PCIe采用了一种叫做De-emphasis的技术,具体细节如下:

· 当前后电平极性变化时,不使用De-emphasis;

· 连续相同极性电平的第一个bit,不使用De-emphasis;

· 只有连续相同极性电平的第一个bit之后的bit,才使用De-emphasis;

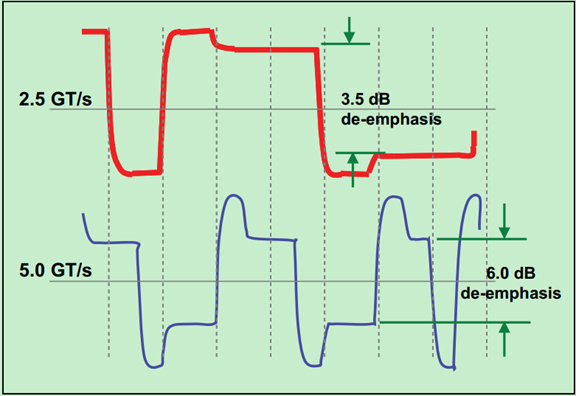

· 对于2.5GT/s,De-emphasis将电压较少3.5dB。对于5GT/s,则是6dB;

· Beacon信号也需要进行De-emphasis,但是规则稍有差别。

注:Beacon信号在之前关于LTSSM的文章中介绍过。

如下图所示:

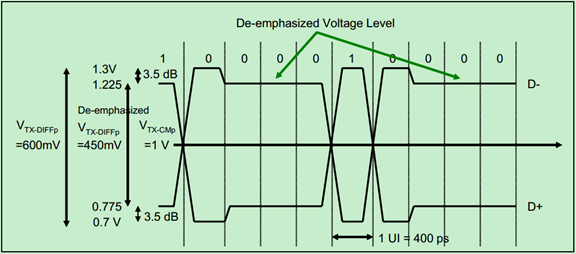

一个De-emphasis的例子如下图所示:

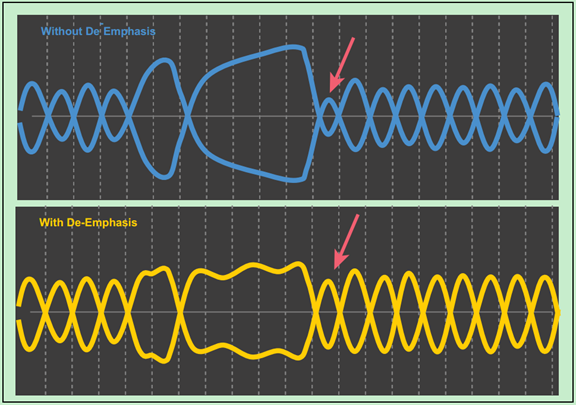

采用De-emphasis之后的PCIe设备接收端信号如下图所示:

差分的例子:

此外,对于部分使用低摆幅(Reduced Swing)的PCIe设备来说,一般不需要使用De-emphasis。考虑到,这种低摆幅的设备一般传输线都比较短(甚至是同一颗芯片/封装里面),介质损耗相对较小。