FPGA定点小数计算(三)——定点与浮点的转换

1赞0 引言

前面的文章中介绍了定点小数的基本格式,乘法和除法运算等。我们知道,定点小数具有消耗资源少,运算速度快等优势;同时也有动态范围小,容易数值溢出等缺陷。虽然定点小数可以满足一些场合下的运算需求,但是对于雷达成像,医学成像,高精度数据采集与分析等场合,仍需要采用浮点数进行运算。

这篇文章来简单地介绍一下IEEE 754规定的浮点小数格式,并聊一聊定点小数转换为浮点小数和浮点小数转换为定点小数的方式。

1 IEEE 754浮点小数

单精度浮点

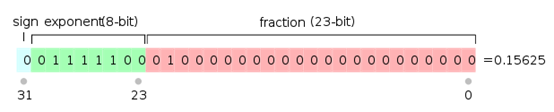

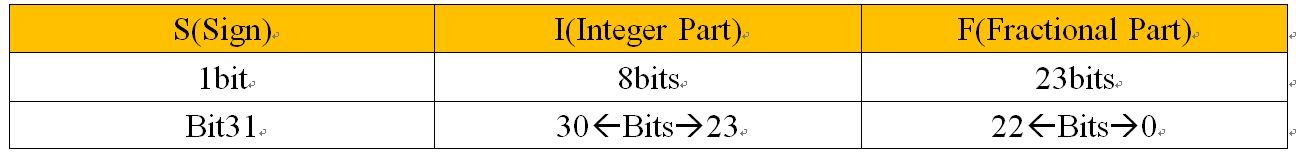

IEEE 754规定单精度浮点(Single Precision Floating-Point)数为32bits,其中最高位为符号位,接着是8bits的指数部分和23bits的小数部分。如下表所示:

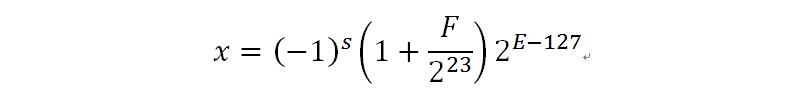

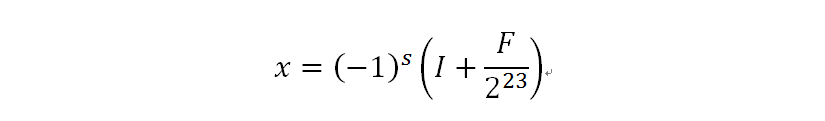

表示的值为:

可表示的值的范围为:±1.18×10−38~ ±3.4×1038 。一个简单的例子如下图所示:

双精度浮点

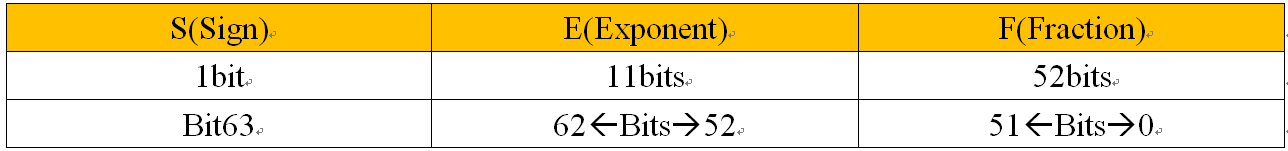

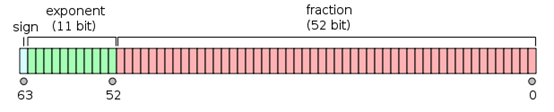

双精度浮点(Double Precision Floating-Point)数为64bits,其中最高位为符号位,接着是11bits的指数部分和52bits的小数部分。如下表所示:

表示的值为:

可表示的值的范围为:±2.23×10−308~ ±1.80×10308 。如下图所示:

此外,IEEE 754还规定了一些特殊数字,如正无穷大(+∞)、负无穷大(-∞)和非数(NaN,Not a Number)等。

下面将以32bit的单精度浮点数为例,简单地介绍一下浮点数与定点数之间的转换方式。定点数的格式(有符号原码数)如下:

则有,

2 定点小数转换为浮点小数

定点小数和浮点小数的小数部分的表示方式是一致的,区别在于:

1) 定点小数存在整数部分,而浮点小数没有整数部分(即整数部分始终为0);

2) 定点小数没有指数部分,而浮点小数存在指数部分(类似于科学计数法)。

因此,定点小数和浮点小数之间的转换的核心是:定点小数的整数部分与浮点小数指数部分之间的转换。

按照上文提到的定点小数格式,如果按照正常移位比较操作的方式,一般需要8个时钟周期才能确保定点小数的整数部分全部被移出;需要23个时钟周期才能保证小数部分的最高位为1。实际上,我们可以采用类似于二分法的方式,这样只需要3个时钟便可完成操作,简要的步骤如下:

1) 如果Fixed[30:23]大于0,则将Fixed[30:0]右移8位;否则判断Fixed[22:11]是否为0,如果为0,则将Fixed[30:0]左移12位,低位补0;

2) 如果Fixed[22:17]等于0,则将Fixed[30:0]左移6位,低位补0;

3) 如果Fixed[22:20]等于0,则将Fixed[30:0]左移3位,低位补0;

4) 最后根据Fixed[22:20]的值,便可确定浮点小数的指数部分和小数部分的值。

3 浮点小数转换为定点小数

浮点小数转换为定点小数很简单,一般只需要一个时钟周期便可以完成。简要的步骤如下:

1) 如果Float[30:23]小于等于127,则将Float[22:0]右移127-Float[30:23]位;否则将Float[22:0]左移Float[30:23]-127位,低位补0;

2) 然后根据移位后的Float_shift[30:0]便可确定定点小数的整数部分和小数部分。