PCIe扫盲——高级错误报告AER(二)

1赞连载目录篇:http://blog.chinaaet.com/justlxy/p/5100057779

这一篇文章讲一讲,高级错误报告(Advanced Error Reporting,AER)关于可校正和不可校正错误的相关寄存器,以及Root如何处理来自其他PCIe设备的错误消息等内容。

Ø 高级可校正错误处理(Advanced Correctable Error Handling)

高级可校正错误状态寄存器如下图所示,当相关错误发生后,硬件会自动地将对应bit置1。软件可以通过向对应bit写1,来清零。

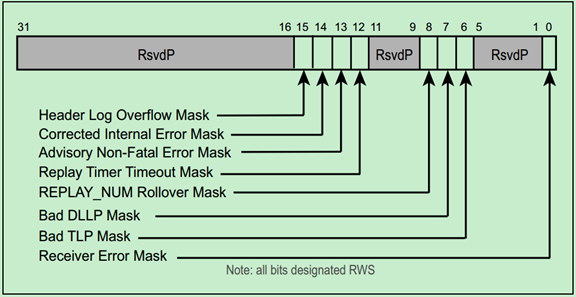

o 高级可校正错误屏蔽

高级可校正错误屏蔽寄存器如下图所示,默认情况下,这些bit的值都是0。也就是说,只要发生相关错误,且该错误报告功能被使能,则相关错误便会被报告(不被屏蔽)。当然,软件可以通过将相关bit置1,来屏蔽相关的错误报告信息。

Ø 高级不可校正错误处理(Advanced Uncorrectable Error Handling)

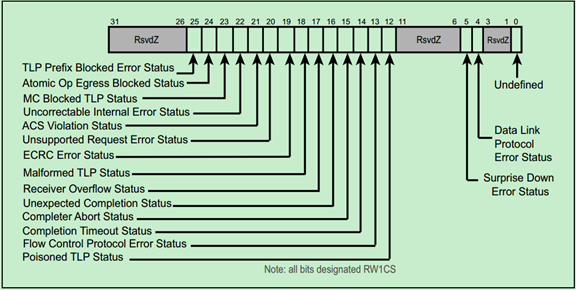

o 高级不可校正错误状态

高级不可校正错误状态寄存器如下图所示,当相关错误发生时,不管这些错误会不会被报告到Root,相关的bit都会被置1。

回顾一下,前一篇文章中的当前错误指针(First Error Pointer)。假设该指针的值为18d,则表明不可校正错误状态寄存器中的第18位对应的错误——异常的TLP(Malformed TLP)将会被最先处理。一旦该错误被处理后,软件将会向不可校正错误状态寄存器的第18位写1,来清除该bit。然后,当前错误指针将会被更新到下一个值。

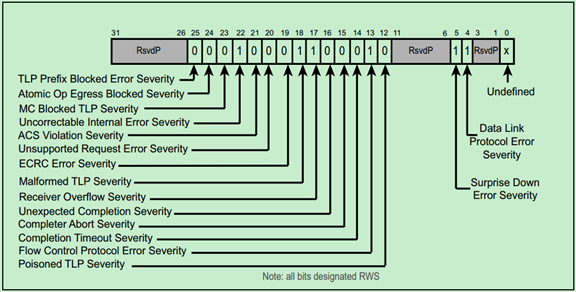

软件可以通过高级不可校正错误严重度寄存器(Advanced Uncorrectable Error Severity Register)来修改不可校正错误是否被作为致命的(Fatal)错误处理,进而使得这些错误得到区分处理。如下图所示,其中,0表示非致命的(Non-Fatal),1表示致命的(Fatal)。

o 高级不可校正错误屏蔽

高级不可校正错误评级寄存器如下图所示,当相关bit被置1时,对应的错误类型将不会被报告。

配置空间中的高级错误报告结构中包含有一个4DW的子空间,用于缓存接收到的,发生不可校正错误的(未被屏蔽的)的TLP的包头。PCIe Spec规定,当设备支持AER功能时,必须有能力至少缓存一个TLP包头(4DW)。当然,有些设备可能支持缓存更多的TLP包头。该子空间被称为包头缓存寄存器(Header Log Register),其支持的错误类型如下图所示。

在PCIe总线拓扑结构中,Root是所有其他PCIe设备错误报告的目标(Target)。当Root接收到来自其他PCIe设备的错误消息(Error Message)后,Root会根据系统的参数设置选择是否向系统报告错误,并以何种方式(中断等)报告。

注:关于PCIe的中断机制会在后续的文章中详细介绍。

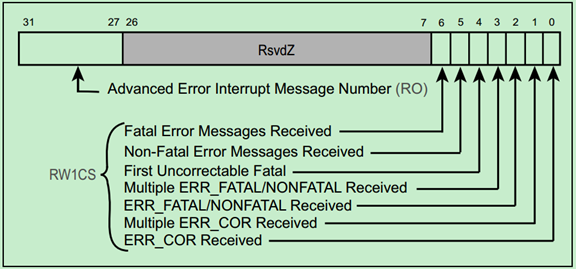

当Root接收到错误消息后,便会将Root错误状态寄存器中的对应位置位。需要注意的时,由于Root自身也是PCIe设备,当其自身发生错误时,也会导致Root错误状态寄存器中的对应位置位,就像是其收到了错误消息了一样。该寄存器如下图所示:

前面的文章介绍过,错误消息也是消息(Message)的一种。错误消息中包含了错误源设备的ID信息(BDF,Bus,Device and Function),根据ID信息,便可以确定错误源的位置等信息,同时将该信息缓存在高级源ID寄存器中,如下图所示。

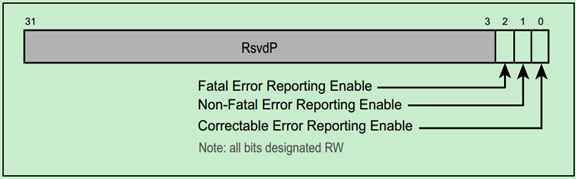

可以通过Root错误命令寄存器(Root Error Command Register)的相关bit来使能或者禁止相关类型的错误是否被报告至系统。如下图所示: