Vivado Logic Analyzer的进一步探讨

0赞

发表于 9/22/2014 11:16:07 PM

阅读(6172)

本文基于Vivado 2014.2,代码基于文章http://blog.chinaaet.com/detail/37239中使用的代码。

这一篇仅讨论在综合后的Netlist中选择信号进行捕获的方法。

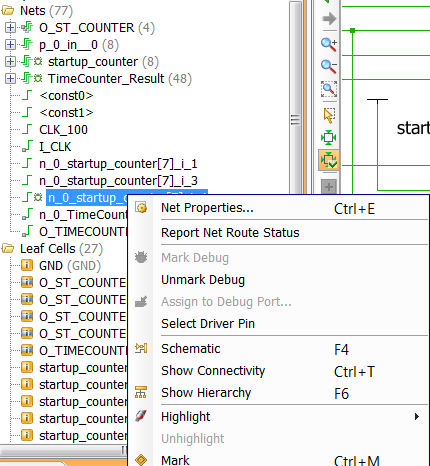

第一个问题就是,只有Nets下的信号可以设置mark debug。

从原理上来说是很不合理的。Chipscope的捕获界面中,只有Reg信号可以被抓取,而Vivado是Net,从实际的角度说也是很不合理的,LUT可以直接被抓去,从原理上和时序上,对设计都是不合适的。

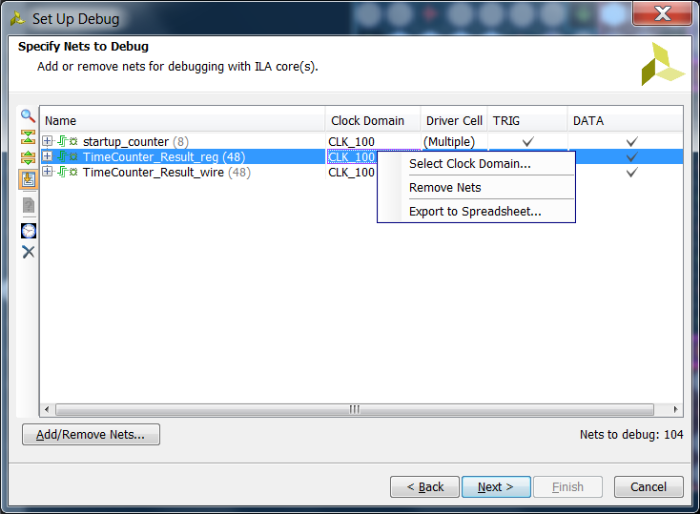

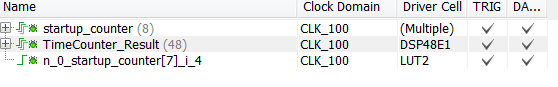

在Set Up Debug中,工具会自动分析信号的所在时钟域,并添加时钟。少数情况,可以通过右键点击Select Clock Domain来修改时钟域。

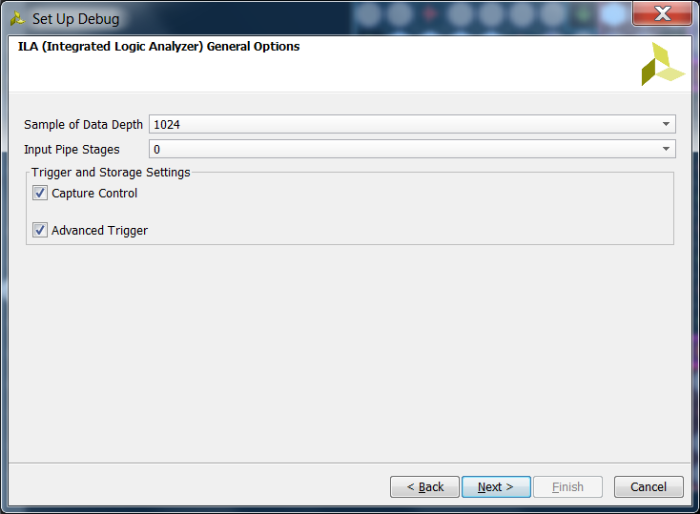

下一页设置存储深度,相比较ChipScope,信号的宽度不需要事先设定好,而是根据捕获信号来自动设定,Vivado确实方便了很多。

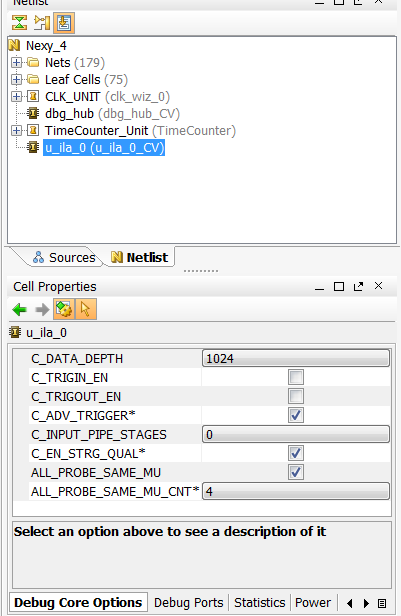

设置好之后,可以在属性中修改ILA Core的属性。确认无误后进行Implementation。

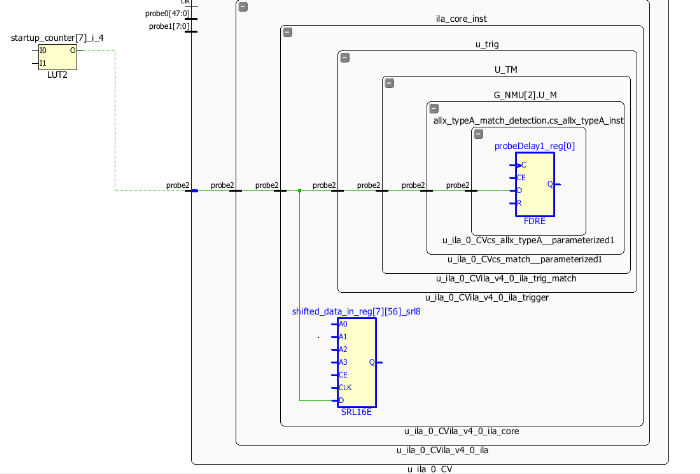

不过,从Implementation的结果可以看到,虽然抓取的是LUT的信号,但是ILA的IP已经添加了寄存器进行隔离。从这一结果考虑,Vivado的ILA设计还是很优秀的。

但即使是这样,为了netlist中的Reg型信号无法设置mark debug,确实是一个不好理解的解释。

最终,Vivado Logic Analyzer的设置会以Tcl脚本的形式反应到XDC文件中。