基于ALTERA实现的4位流水线乘法器

0赞

发表于 5/11/2017 5:24:15 PM

阅读(3402)

本案例:明德扬首创全新FPGA设计技巧--至简设计法,教你如何一步一步去完成一个复杂电路的设计,里面很多有实用技巧,熟练运用这些技巧,有助于你写出非常优秀的FPGA设计代码。非常简洁易读,欢迎比较。

一、功能描述

流水线功能好比一个加工厂在创业之初,只有一间小车间及孤军奋战的老板,那么,当他接到一张订单之后,他必然忙于完成第1张订单,而没有能力去接第2张订单。这样接订单→完成订单→接订单→……是一个串行的过程。后来,老板发现接受订单不费太多时间,而且他还有了一个帮工,他们可以相互独立地工作,这样,老板就在完成上张订单产品的同时,接受下一张订单的订货。而多级流水线的形式,将相邻的两个部分乘积结果再加到最终的输出乘积上,即排列成一个二叉树形式的结构,这样对于N位乘法器需要log2(N)级来实现。本案例用Verilog HDL语言实现了4位流水线乘法器的功能。

二、平台效果图

仿真效果图

三、实现过程

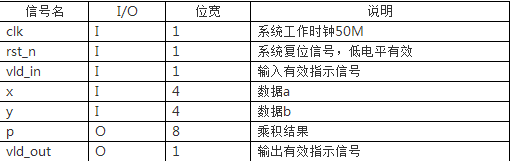

输入输出信号列表如下:

从仿真结果可以看出,上述流水线乘法器比串行乘法器的速度快很多,在非高速的信号处理中有着广泛的应用。

判断x的4位从低到高是否为1,然后对应移位y并并置上对应的0,让其成为一个移位后的8位数据,比如x[2]为1,y为1100,则将y变为00110000,然后将对应的四个数据放入寄存器a0,b0,a1,b1,然后计算tmp0<=a0+b0,tmp1<=a1+b1,然后再p <= {2'b0,tmp0} + tmp1;即可得到最终乘积p。

以此实现了一个4位流水线乘法器。

代码资料下载:http://pan.baidu.com/s/1gePRKZp